Pós-Graduação em Ciência da Computação

“LEDges: nova técnica de inspeção visual

automática para detecção em tempo-real de

irregularidades em bordas”

Por

**Ygo Neto Batista**

Dissertação de Mestrado

Universidade Federal de Pernambuco

[posgraduacao@cin.ufpe.br](mailto:posgraduacao@cin.ufpe.br)

[www.cin.ufpe.br/~posgraduacao](http://www.cin.ufpe.br/~posgraduacao)

Recife-PE, Agosto/2011

Ygo Neto Batista

*LEDges: nova técnica de inspeção visual

automática para detecção em tempo-real de

irregularidades em bordas*

Dissertação apresentada ao Centro de Informática - CIn, da Universidade Federal de Pernambuco - UFPE, como exigência parcial para obtenção do título de mestre em ciências da computação.

Orientador:

Prof. Dr. Cristiano Coelho de Araújo

Co-orientador:

Prof. Dr. Abel Guilhermino da Silva Filho

UNIVERSIDADE FEDERAL DE PERNAMBUCO - UFPE

CENTRO DE INFORMÁTICA - CIn

Recife-PE

Agosto/2011

**Catalogação na fonte

Bibliotecária Jane Souto Maior, CRB4-571**

**Batista, Ygo Neto**

**LEDges: nova técnica de inspeção visual automática

para detecção em tempo-real de irregularidades em

bordas / Ygo Neto Batista - Recife: O Autor, 2011.**

**177 folhas : il., fig., tab.**

**Orientador: Cristiano Coelho de Araújo.**

**Dissertação (mestrado) - Universidade Federal de

Pernambuco. CIn, Ciência da Computação, 2011.**

**Inclui bibliografia e apêndice.**

**1. Engenharia da computação. 2. Sistemas embarcados. I.

Araújo, Cristiano Coelho de (orientador). II. Título.**

**621.39**

**CDD (22. ed.)**

**MEI2011 – 115**

*Que ninguém se engane:

só se consegue a simplicidade através de muito trabalho.*

—CLARICE LINSPECTOR (A paixão segundo G.H.)

Dissertação de mestrado sob o título “*LEDges: nova técnica de inspeção visual automática para detecção em tempo-real de irregularidades em bordas*”, defendida por Ygo Neto Batista e aprovada em 30 de agosto de 2011, em Recife, Estado de Pernambuco, pela banca examinadora constituída pelos doutores:

---

Prof. Dr. Cristiano Coelho de Araújo

Orientador

---

Prof. Dr. Adriano Augusto de M. Sarmento

Universidade Federal de Pernambuco —

UFPE

---

Prof. Dr. Isnaldo José de Souza Coêlho

Universidade Federal do Vale do São

Francisco — UNIVASF

## ***Agradecimentos***

Primeiramente agradeço a Deus por ter me dado a oportunidade de elaborar esta dissertação. Aos meus pais, Carlos e Dalva, e à minha esposa, Suzana, pelo amor, carinho, compreensão e respeito, antes e durante a elaboração deste trabalho. Aos meus orientadores, professores Cristiano de Araújo e Abel Guilhermino, que me acompanharam pacientemente e, de fato, me orientaram nessa caminhada. Ao professor Isnaldo Coêlho, pela presteza e interesse em conhecer a minha dissertação. Aos amigos Rafael Macieira e Ricardo Lins, pelas valiosas contribuições no desenvolvimento inicial, e ao primo e amigo Rafael Neto, no desenvolvimento final do trabalho. À empresa Optanica Soluções Fotônicas Ltda., por acreditar na idéia proposta e investir recursos na infraestrutura para seu desenvolvimento. Aos amigos Antonio Vaz e Roberta Souza, pelo apoio incondicional.

## *Resumo*

Este trabalho apresenta uma nova técnica de inspeção visual automática para detecção, em tempo real, de deformações em bordas (LEDges), uma aplicação e duas implementações desta técnica: uma baseada em microcontrolador e outra, em FPGA. A principal inovação da LEDges é um novo modelo de iluminação estruturada que torna mais fácil a segmentação pela limiarização da imagem do objeto sob inspeção. Esta técnica, além de reduzir显著mente o esforço computacional para executar a segmentação, representação e descrição da imagem, também reduz o uso de recursos computacionais, tais como processador e memória. Adicionalmente, a LEDges pode ser implementado em diversas arquiteturas. Esta flexibilidade permite a construção de sistemas de inspeção visual automáticos satisfazendo a demanda crescente por desempenho, com menor tempo de resposta e menor uso de recursos computacionais quando comparados a outras soluções de mesma complexidade computacional. A LEDges foi implementada e aplicada a um problema industrial real onde defeitos foram detectados com sucesso em bordas de tubos de creme dental.

# *Abstract*

This work presents a new automatic visual inspection technique for real time flaw detection on edges (LEDges), an application and two implementations of this technique: one based on a microcontroller and another, on a FPGA. The main innovation of the LEDges is a new structured illumination model, which makes easier the segmentation by binarization of the object under inspection image. This, on one hand, significantly reduces the computational effort to perform the image segmentation, representation and description. On the other hand reduces the use of costly architectural resources such as processor and memory. Furthermore the LEDges can be implemented in different architectures. This flexibility allows the implementation of automatic visual inspection systems satisfying the increasing demand for performance with lower response time and lower use of computational resources when compared to the other solutions with same computational complexity. The solution was implemented and applied to a real industrial problem where defects were successfully detected in the edges of toothpaste tubes.

# ***Lista de Figuras***

|    |                                                                                                                                                                                               |       |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1  | Etapas de processamento de um sistema de IVA típico. . . . .                                                                                                                                  | p. 23 |

| 2  | Arquitetura típica de um sistema de IVA. . . . .                                                                                                                                              | p. 28 |

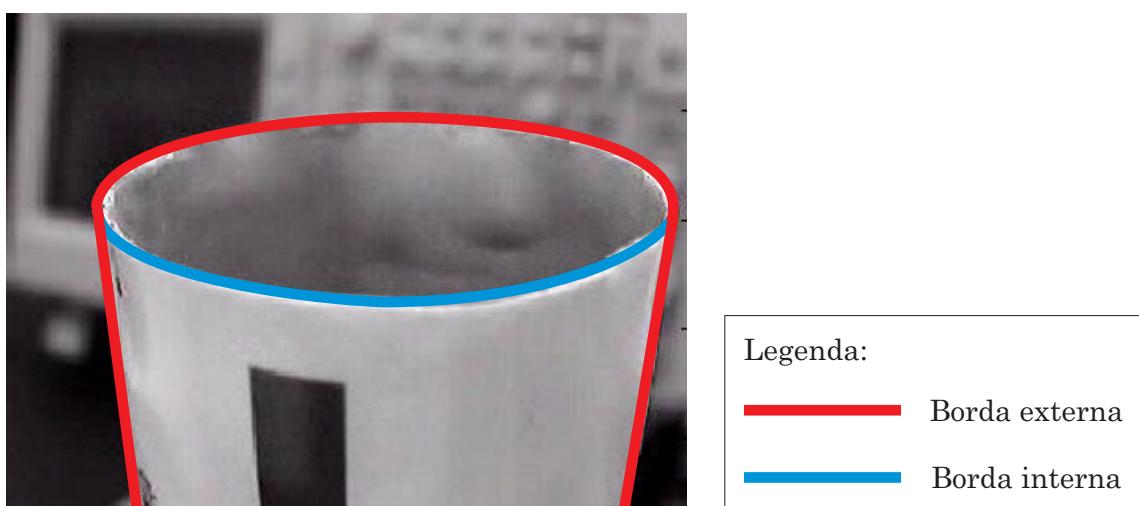

| 3  | Bordas externas e interna de um tubo de creme dental. . . . .                                                                                                                                 | p. 38 |

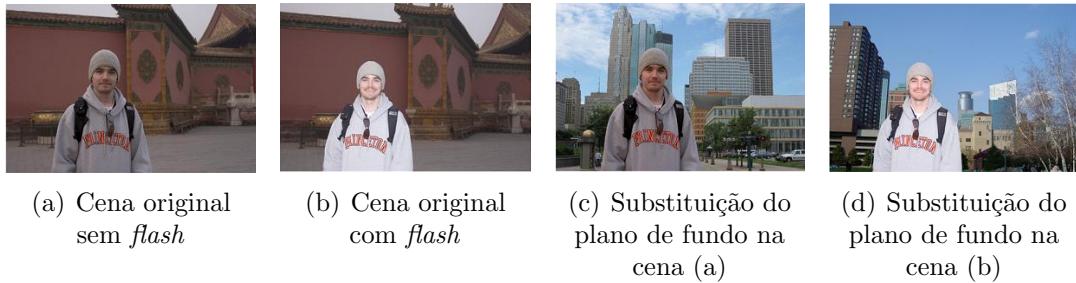

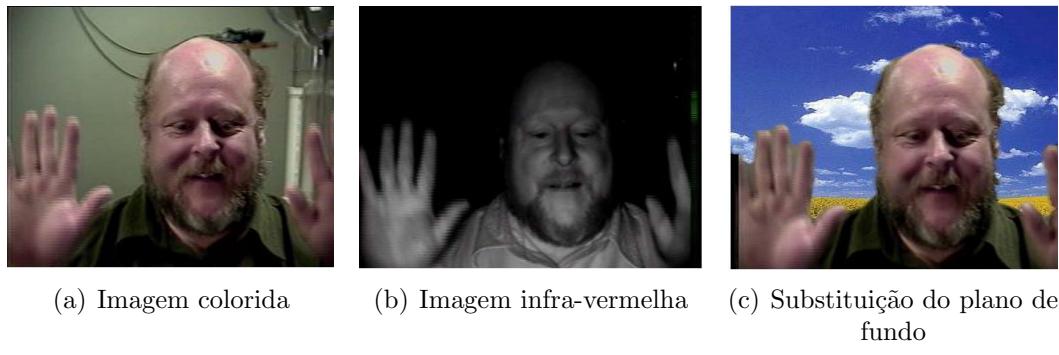

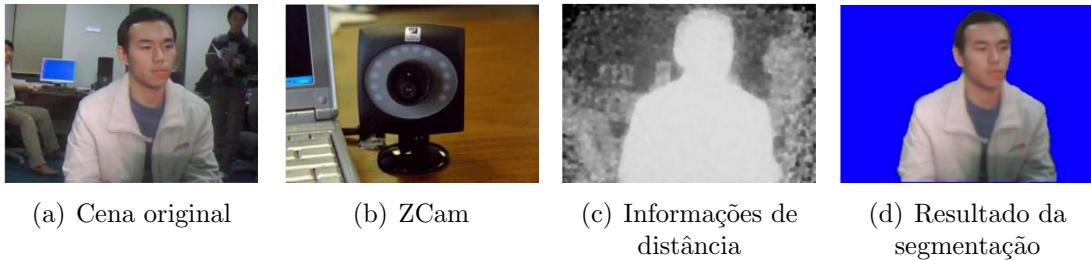

| 4  | Imagens adquiridas seqüencialmente sem (a) e com (b) <i>flash</i> . Resultado da aplicação da técnica (c,d) posicionando o primeiro plano da cena original em novos planos de fundo . . . . . | p. 40 |

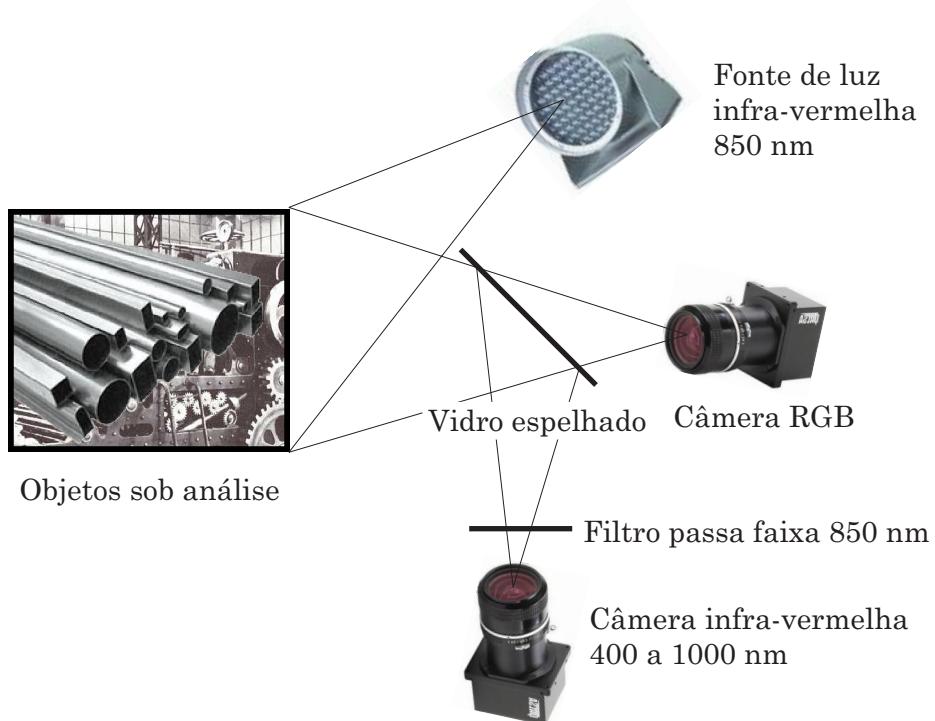

| 5  | Arquitetura do sistema de aquisição das imagens . . . . .                                                                                                                                     | p. 40 |

| 6  | Um exemplo de segmentação. Em (a) e (b) as imagens adquiridas. Em (c) o resultado da segmentação da imagem com substituição do plano de fundo original . . . . .                              | p. 41 |

| 7  | Imagens adquiridas com iluminação infra-vermelha no plano de fundo. .                                                                                                                         | p. 41 |

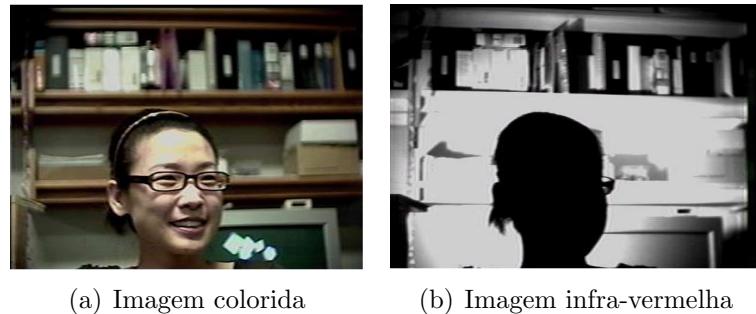

| 8  | Utilização da informação de profundidade para segmentação do primeiro plano. . . . .                                                                                                          | p. 42 |

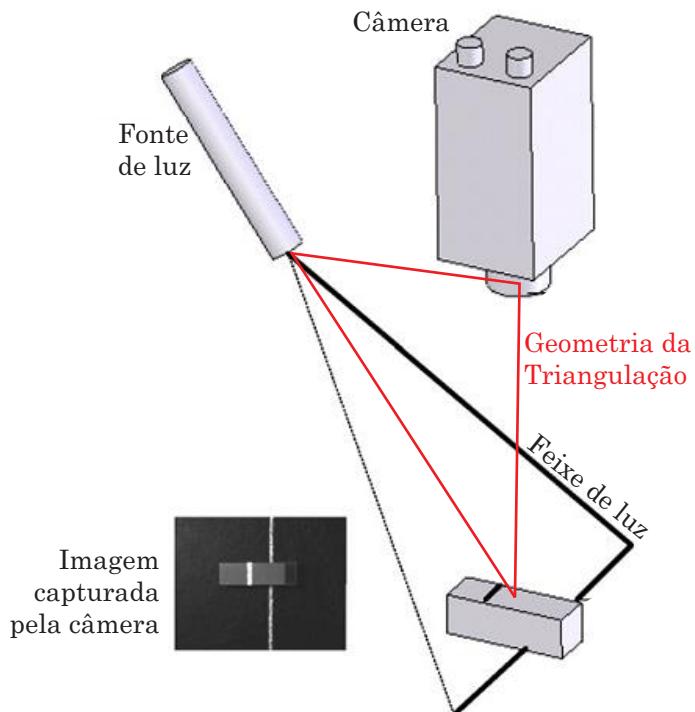

| 9  | Geometria da triangulação. . . . .                                                                                                                                                            | p. 44 |

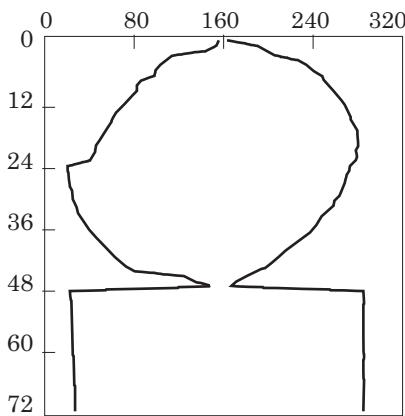

| 10 | Geração de uma assinatura. . . . .                                                                                                                                                            | p. 44 |

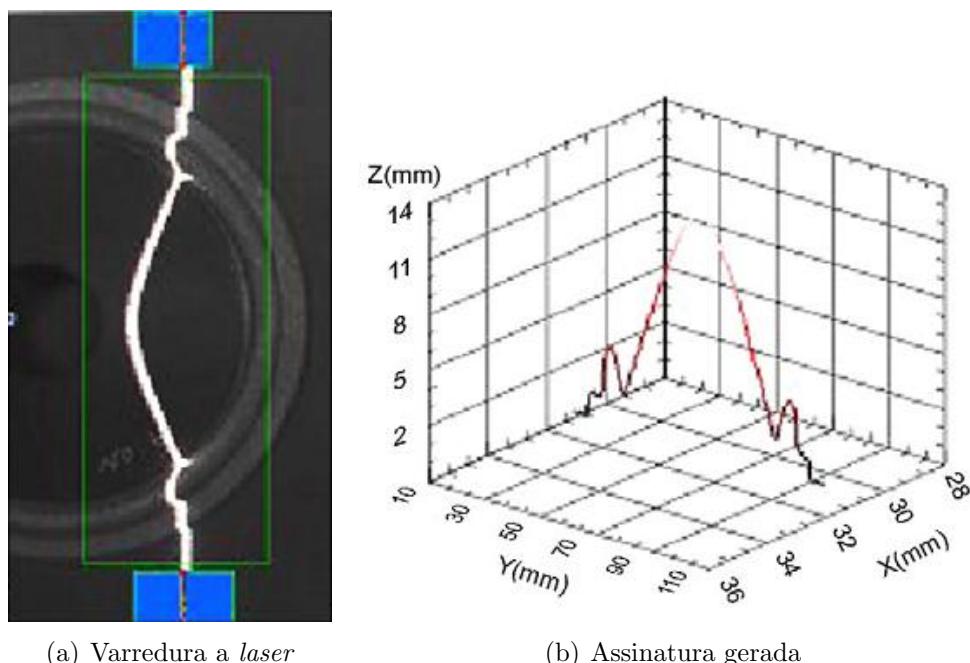

| 11 | Aquisição da imagem, área de inspeção e detecção das bordas da boca da garrafa. . . . .                                                                                                       | p. 47 |

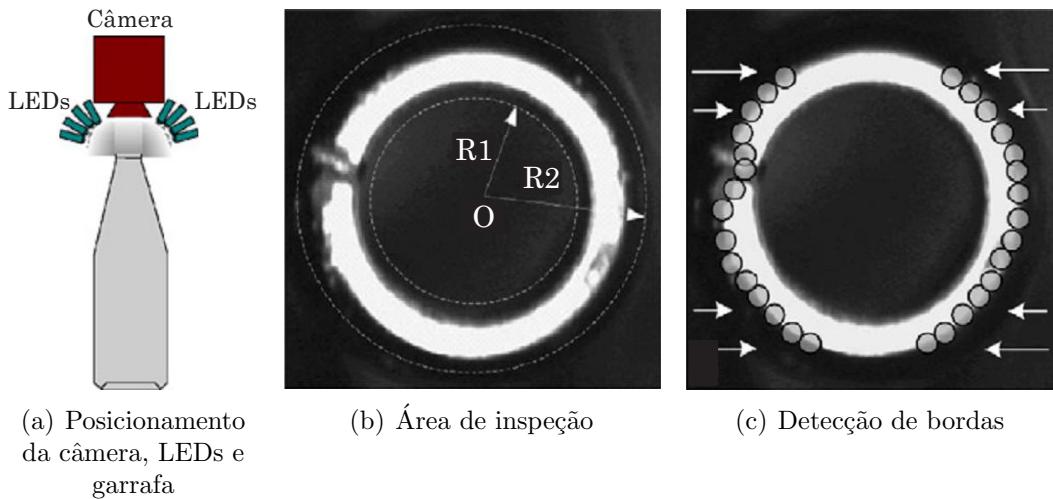

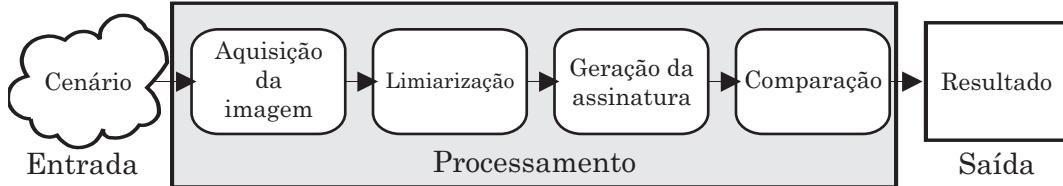

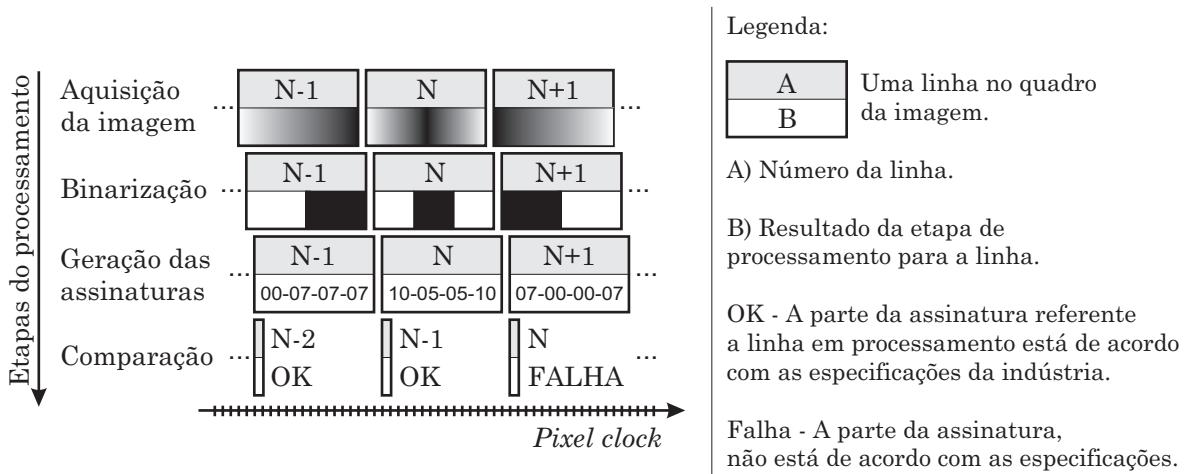

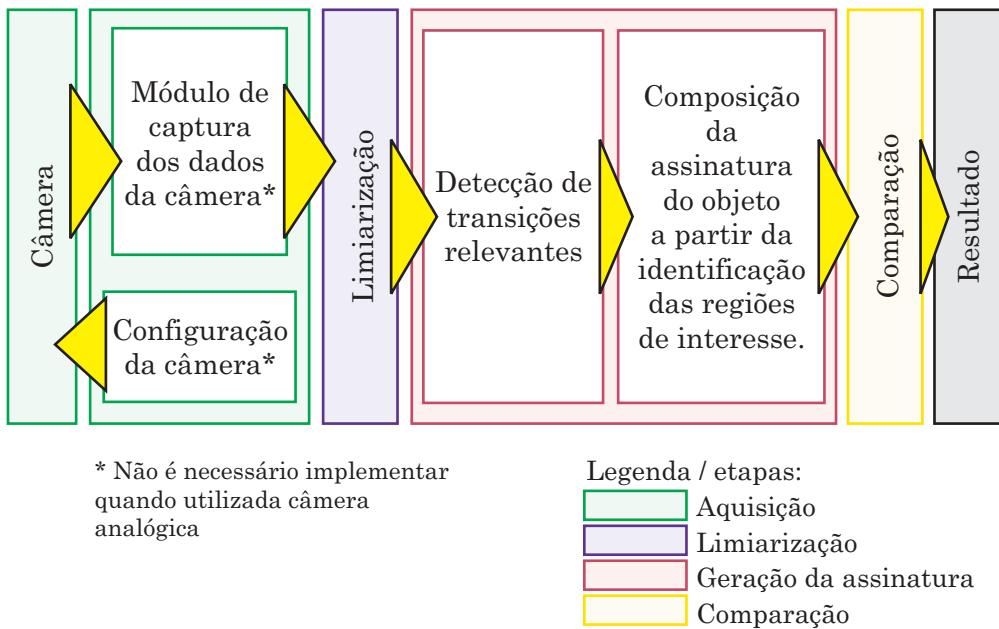

| 12 | Etapas do processamento da LEDges. . . . .                                                                                                                                                    | p. 52 |

| 13 | Fluxo de informações entre as etapas do processamento da LEDges. . .                                                                                                                          | p. 53 |

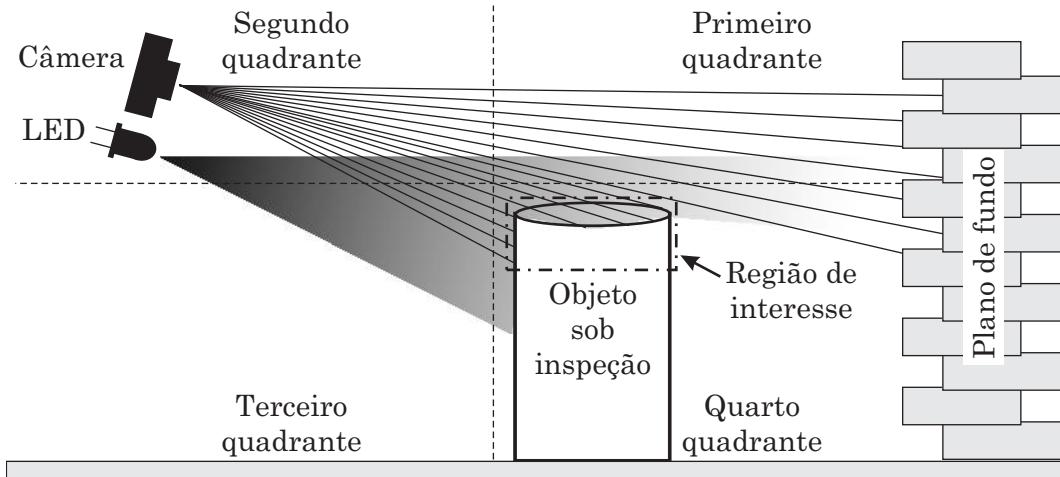

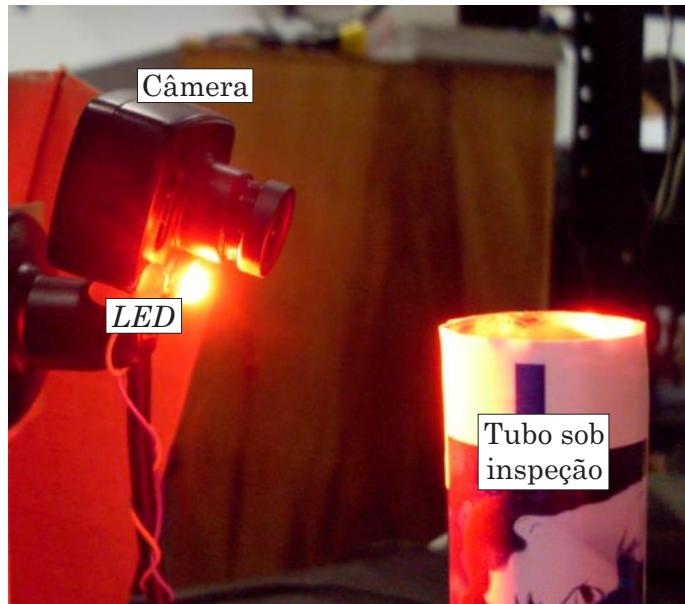

| 14 | Posicionamento da câmera, <i>LED</i> , objeto sob inspeção e cenário. . . .                                                                                                                   | p. 54 |

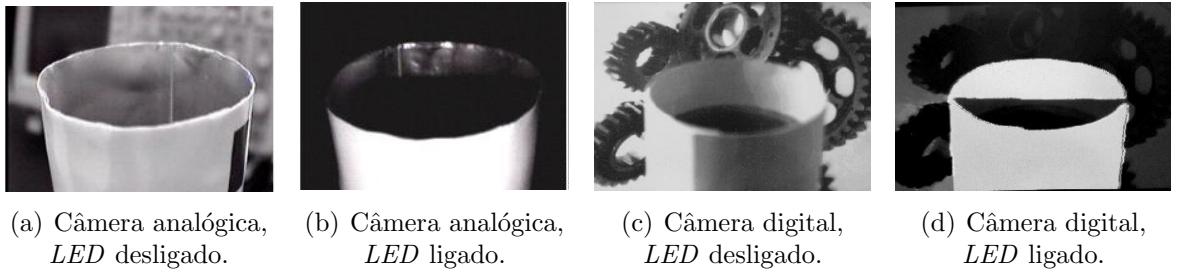

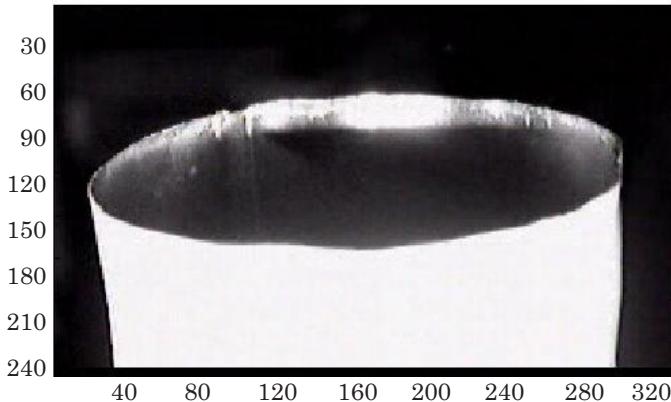

| 15 | Imagens adquiridas. . . . .                                                                                                                                                                   | p. 56 |

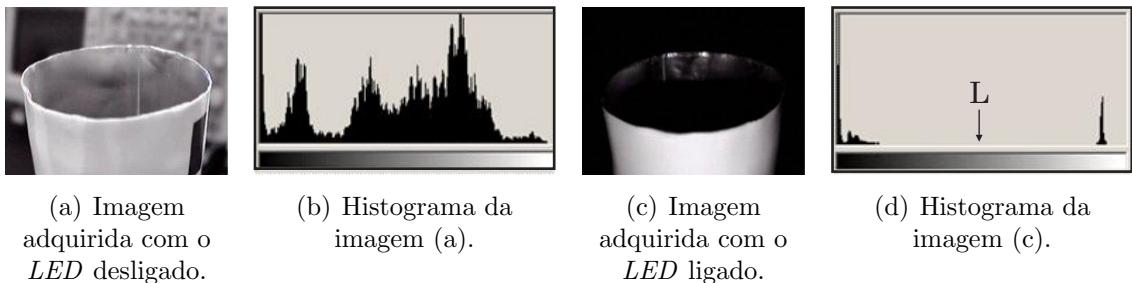

| 16 | Imagens adquiridas e seus histogramas. . . . .                                                                                                                                                | p. 56 |

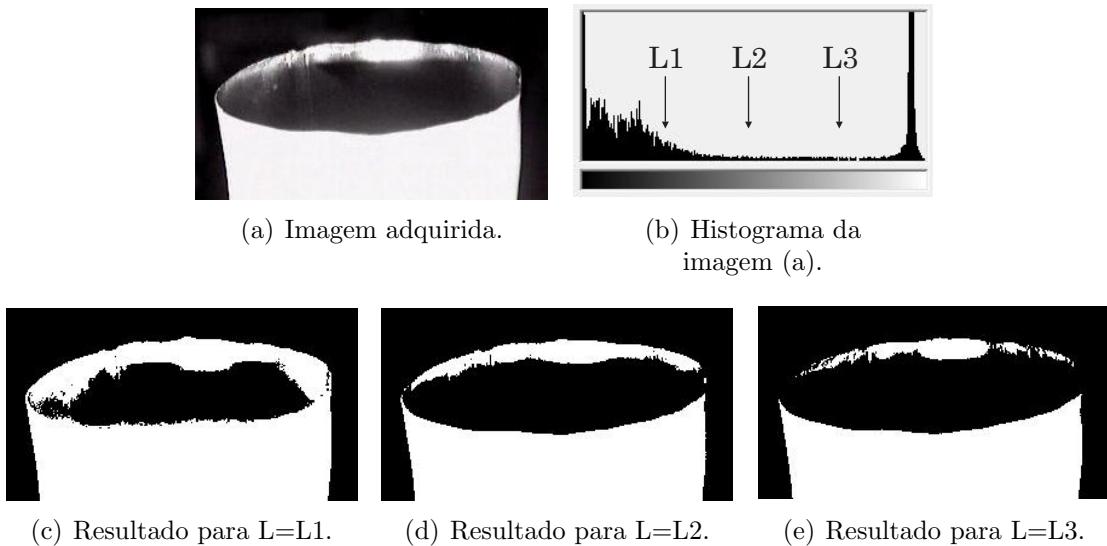

| 17 | Entrada e saídas da etapa de limiarização. . . . .                                                                                                                                            | p. 58 |

|    |                                                                                                                                          |       |

|----|------------------------------------------------------------------------------------------------------------------------------------------|-------|

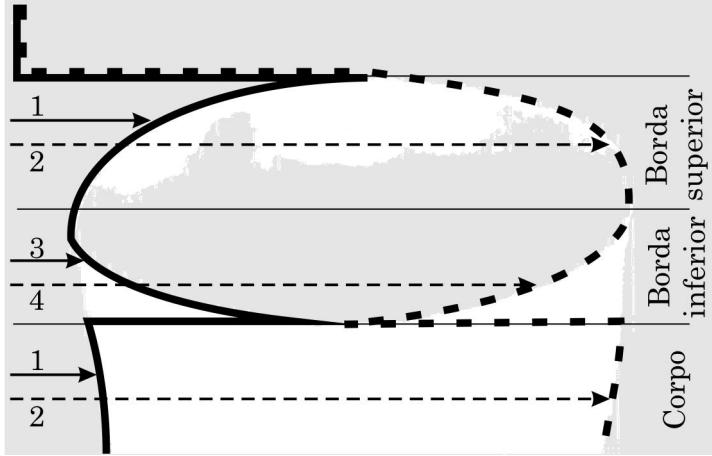

| 18 | Transições relevantes da imagem e que formarão a assinatura do tubo. . .                                                                 | p. 59 |

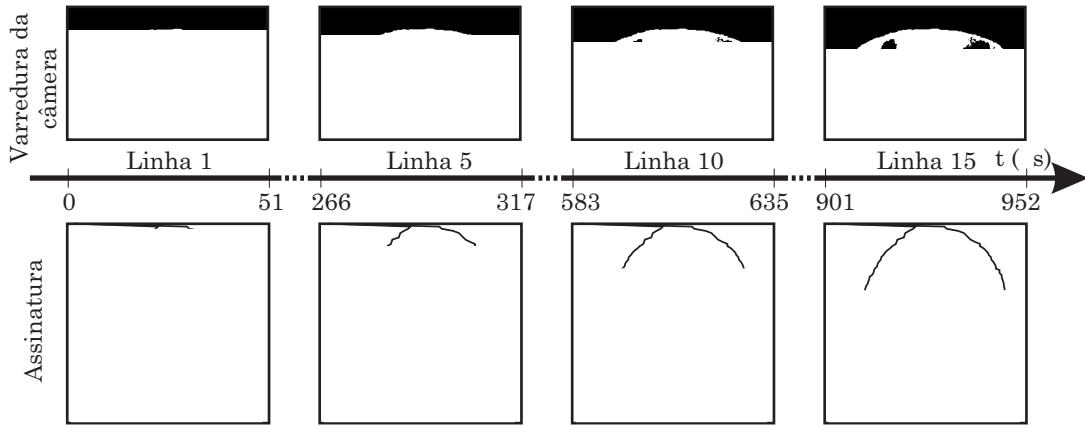

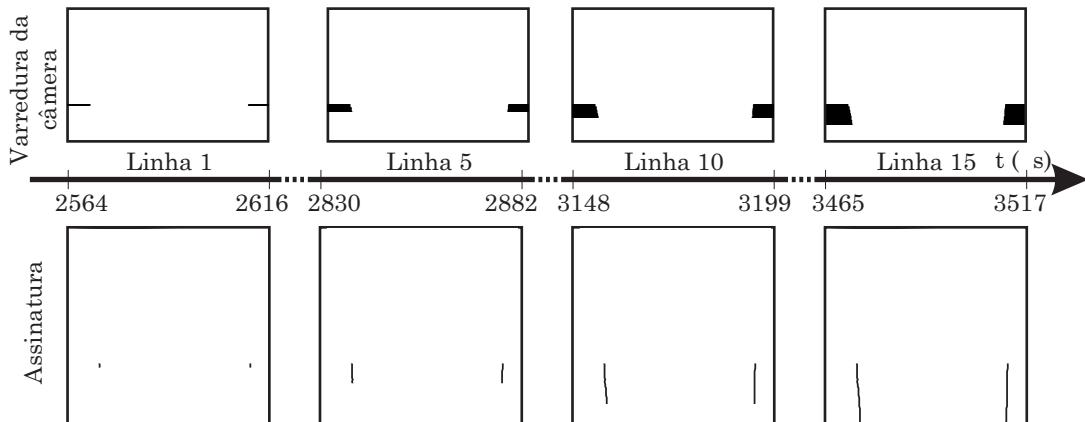

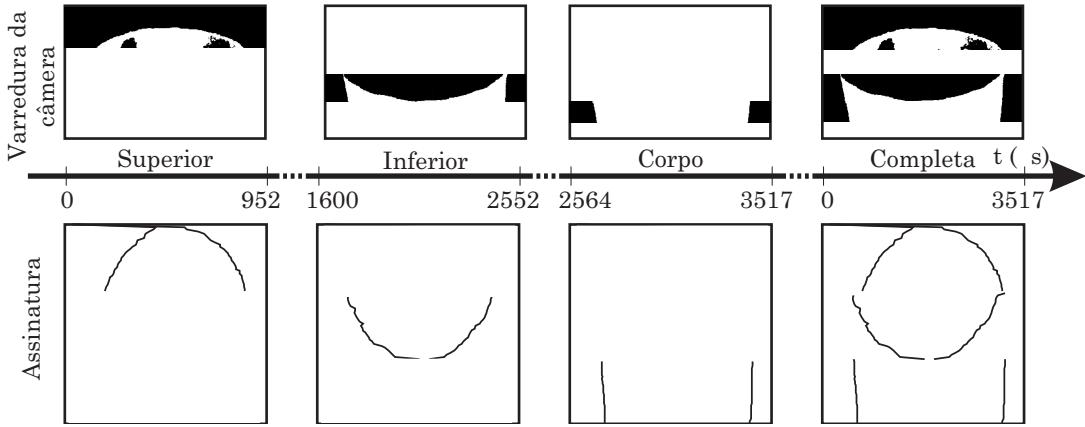

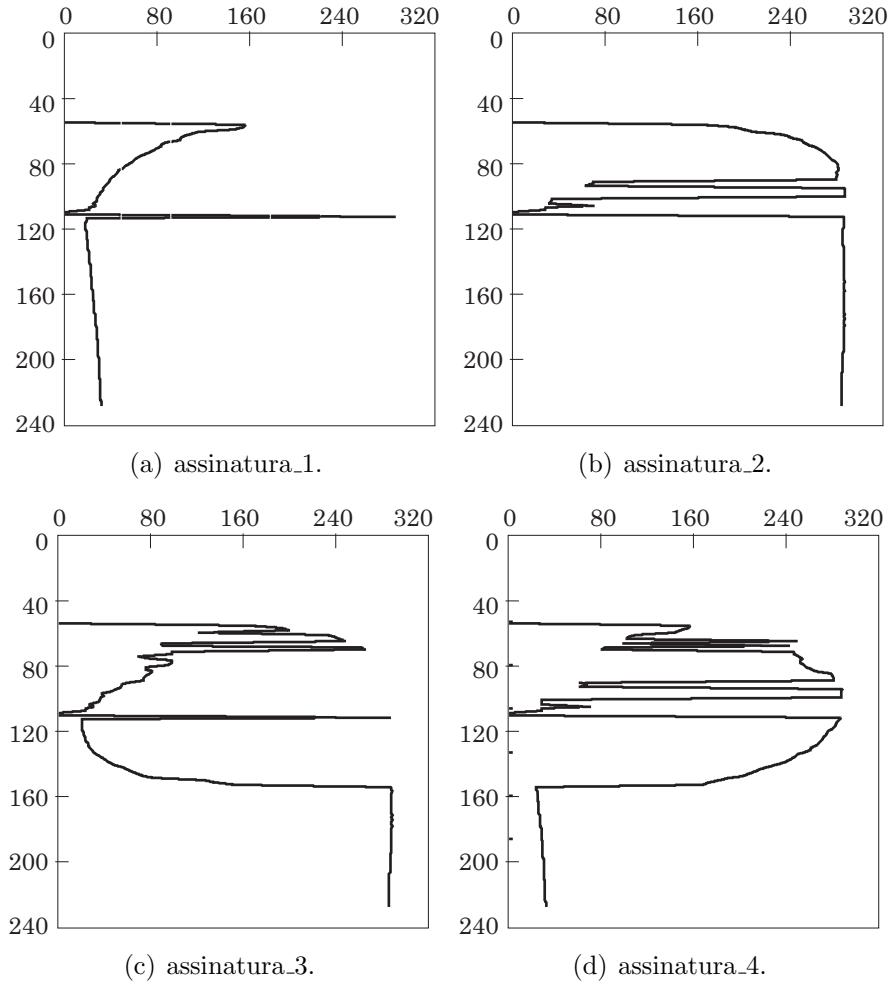

| 19 | Geração das assinaturas da borda superior do tubo. . . . .                                                                               | p. 60 |

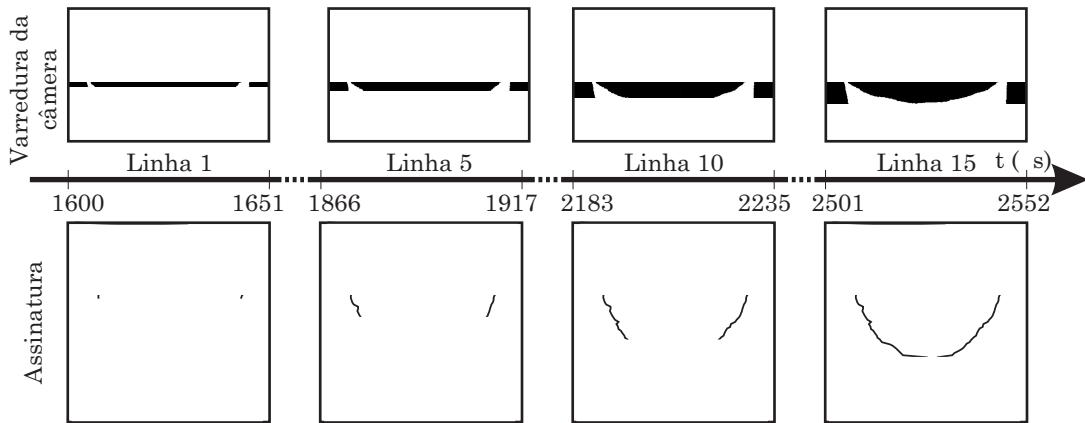

| 20 | Geração das assinaturas da borda inferior do tubo. . . . .                                                                               | p. 60 |

| 21 | Geração das assinaturas do corpo do tubo. . . . .                                                                                        | p. 60 |

| 22 | Composição das assinaturas completas do tubo. . . . .                                                                                    | p. 61 |

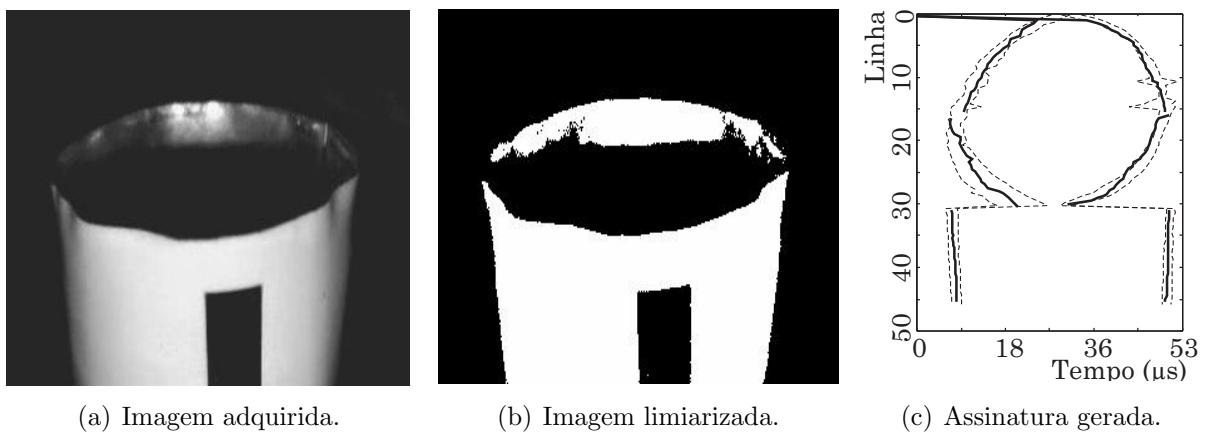

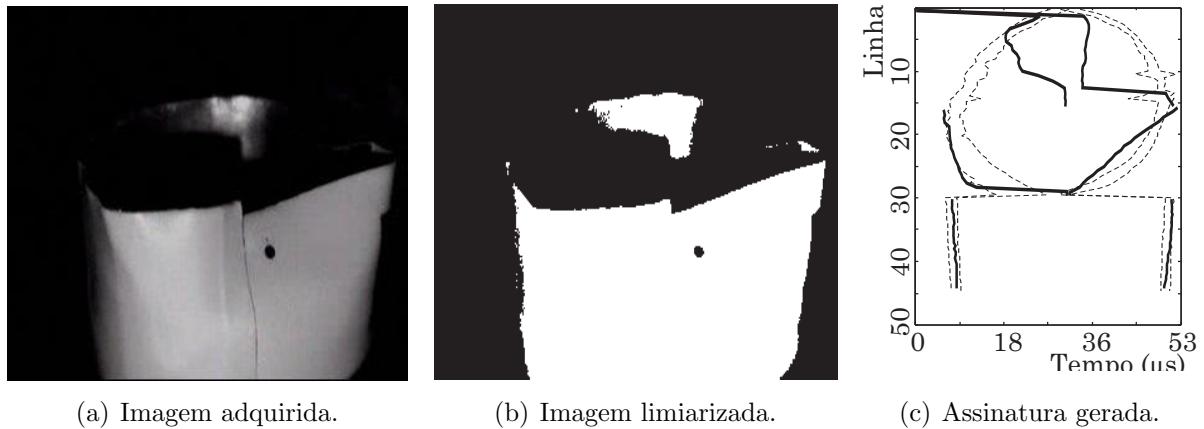

| 23 | Resultado da etapa de geração da assinatura para um tubo amassado. .                                                                     | p. 61 |

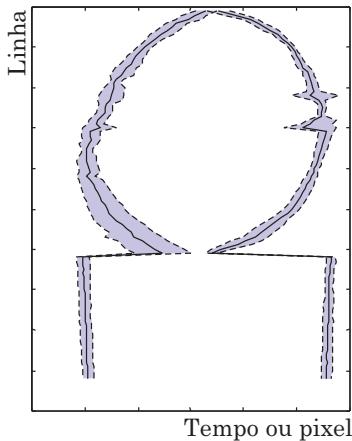

| 24 | Média de assinaturas de dez objetos “bons” $\pm$ tolerância baseada no desvio padrão. . . . .                                            | p. 62 |

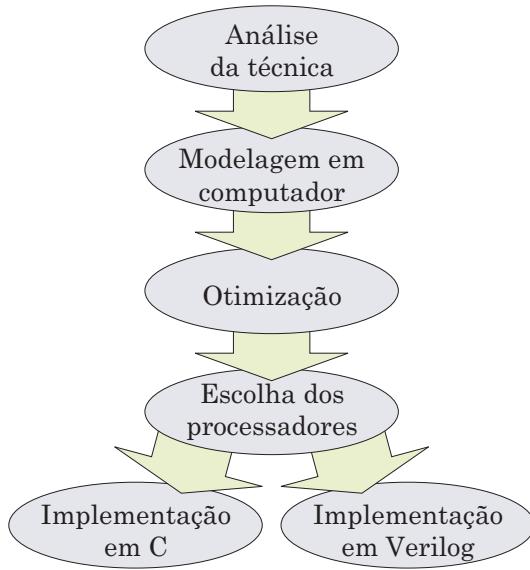

| 25 | Fluxo para definição das arquiteturas. . . . .                                                                                           | p. 67 |

| 26 | Diagrama em blocos para avaliação das arquiteturas. . . . .                                                                              | p. 68 |

| 27 | Imagen adquirida e armazenada no computador. . . . .                                                                                     | p. 69 |

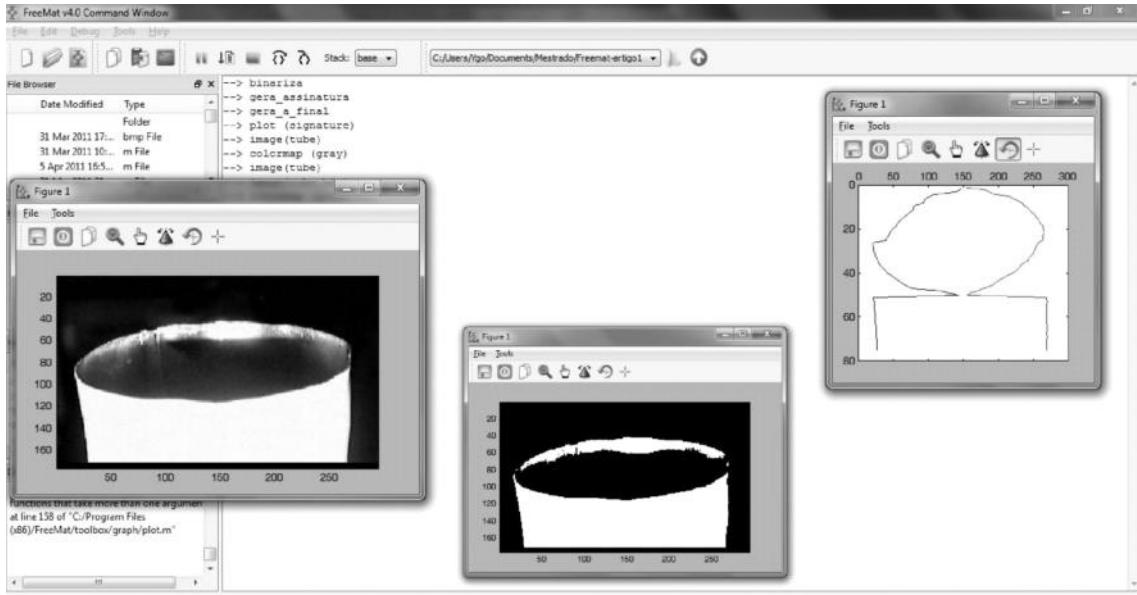

| 28 | Tela do FreeMat. . . . .                                                                                                                 | p. 70 |

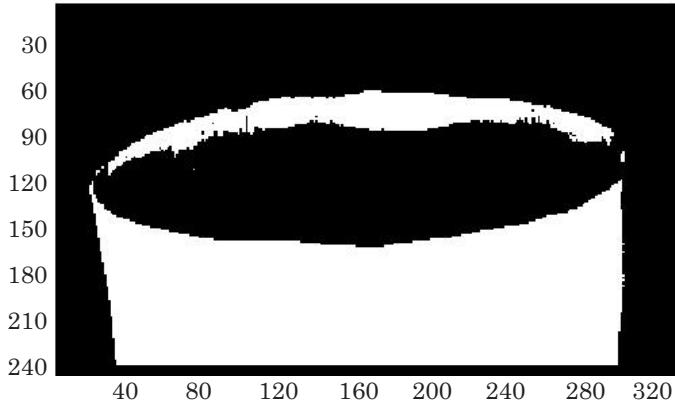

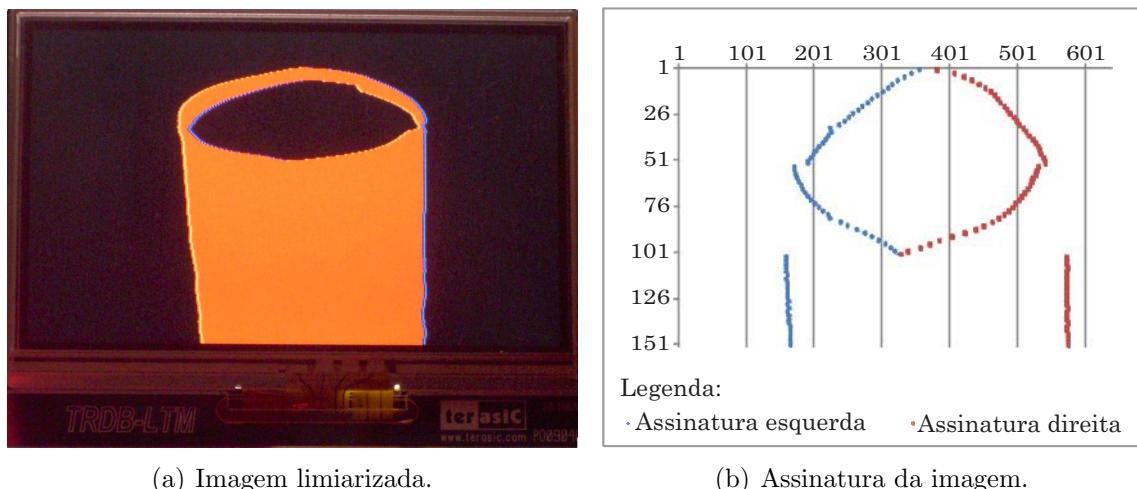

| 29 | Imagen limiarizada. . . . .                                                                                                              | p. 70 |

| 30 | Vetores armazenados plotados. . . . .                                                                                                    | p. 71 |

| 31 | Matriz da assinatura final plotada. . . . .                                                                                              | p. 72 |

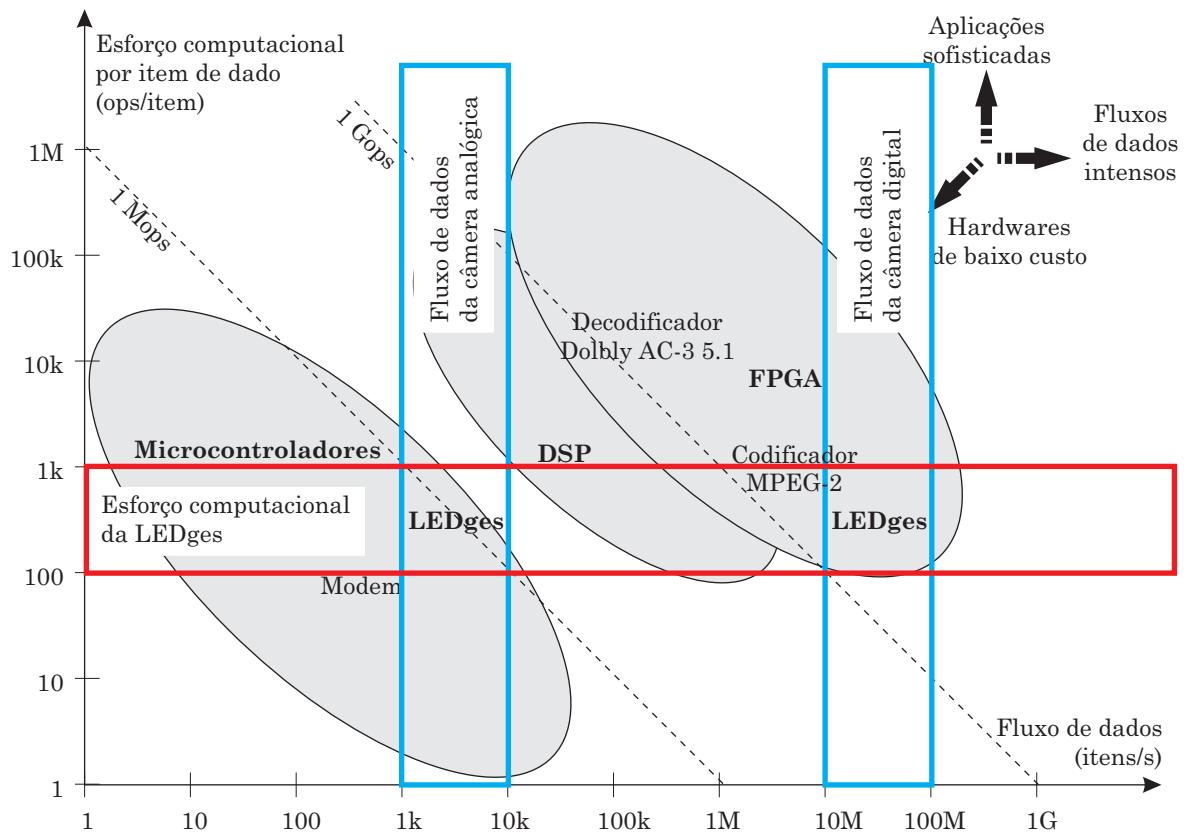

| 32 | Relação entre fluxo de dados, esforço computacional e custo das soluções para a implementação da LEDges. Adaptado de Kaeslin(1). . . . . | p. 76 |

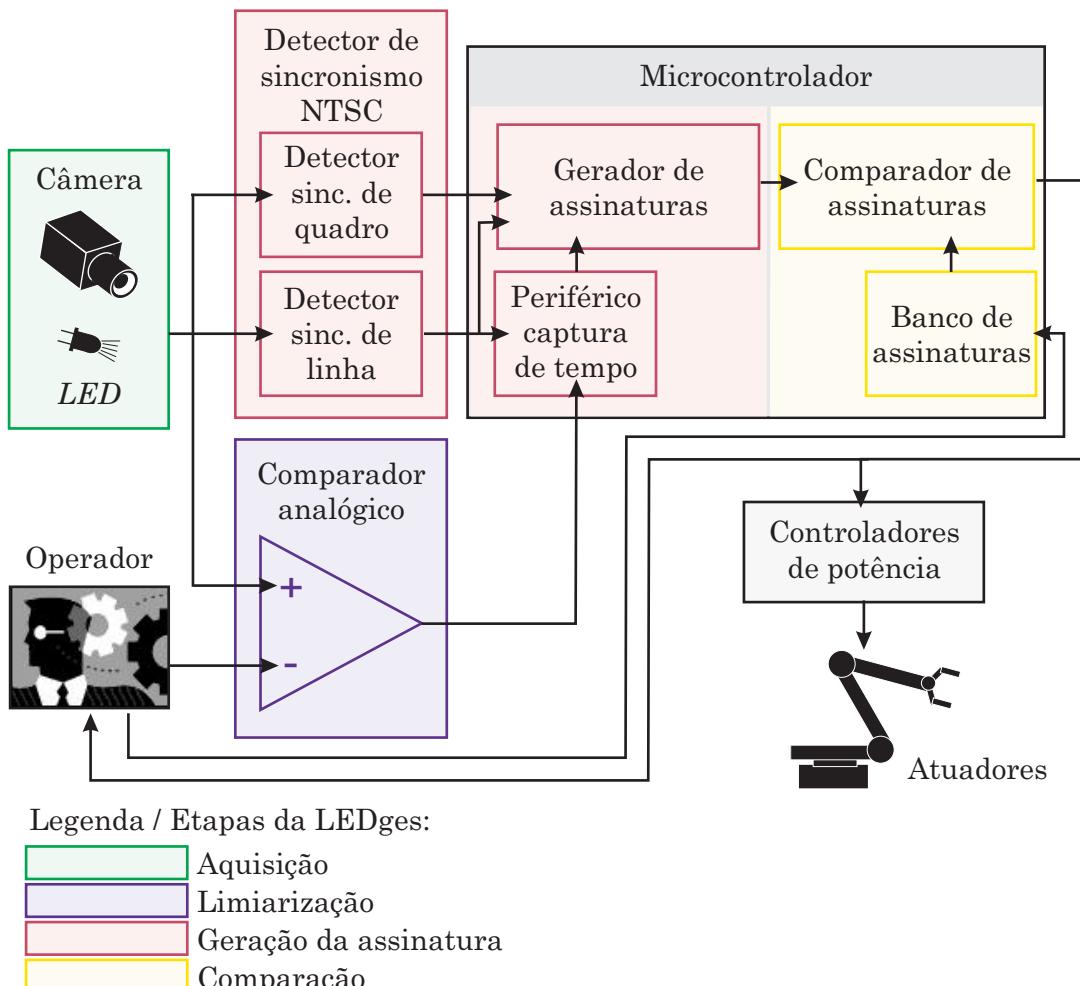

| 33 | Diagrama em blocos. . . . .                                                                                                              | p. 79 |

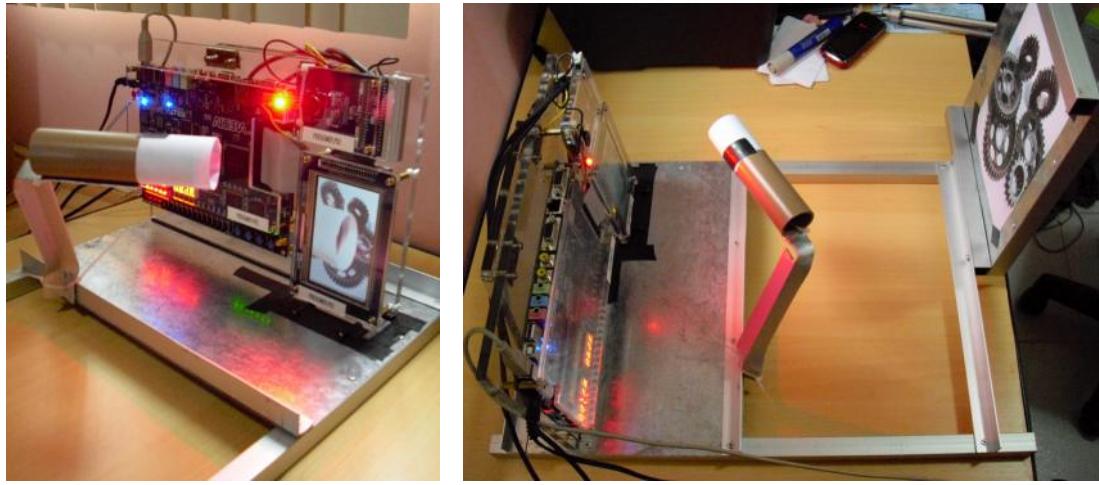

| 34 | <i>Hardware</i> para aquisição da imagem. . . . .                                                                                        | p. 81 |

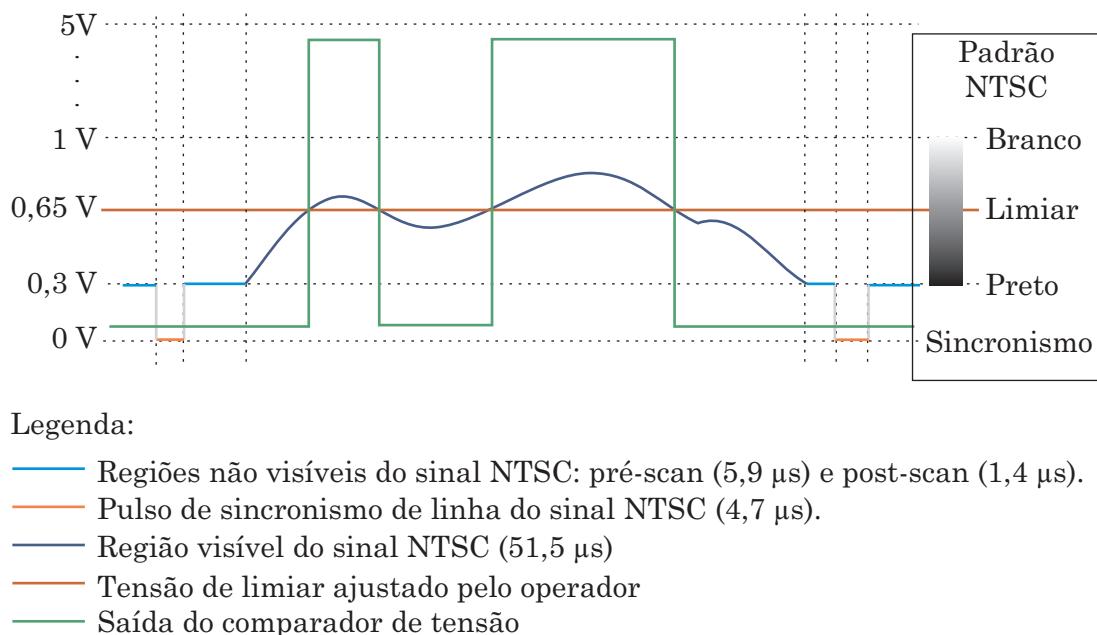

| 35 | Sinal adquirido padrão NTSC e saída limiarizada. . . . .                                                                                 | p. 82 |

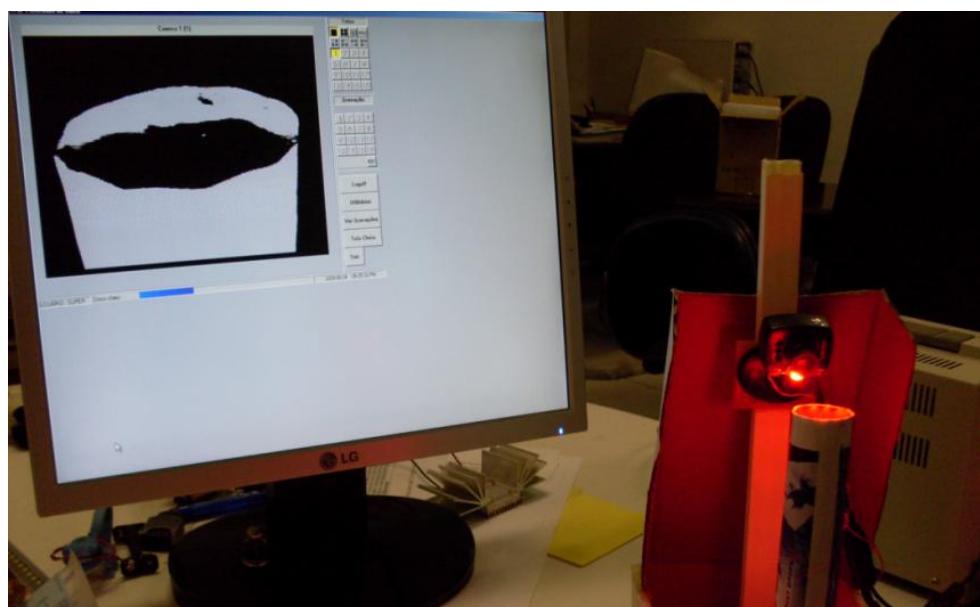

| 36 | Imagen limiarizada observada em um PC. . . . .                                                                                           | p. 82 |

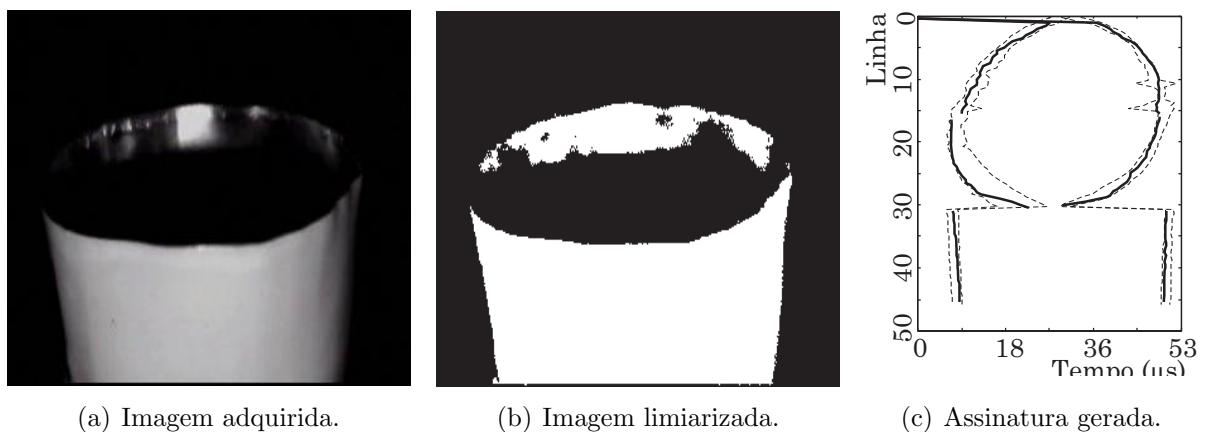

| 37 | Tubo “bom” 1. . . . .                                                                                                                    | p. 85 |

| 38 | Tubo “bom” 2. . . . .                                                                                                                    | p. 85 |

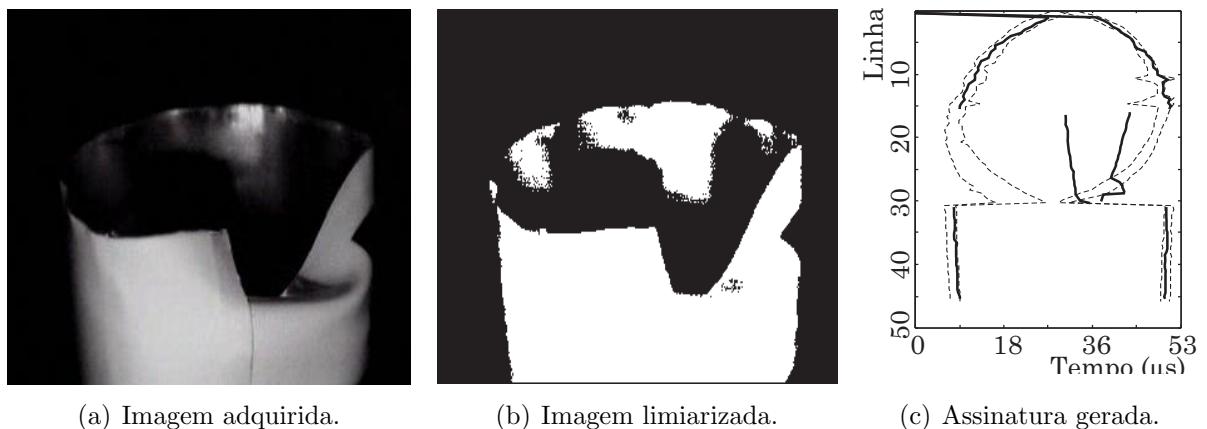

| 39 | Tubo amassado 1. Imperfeição detectada na região da assinatura inferior.                                                                 | p. 86 |

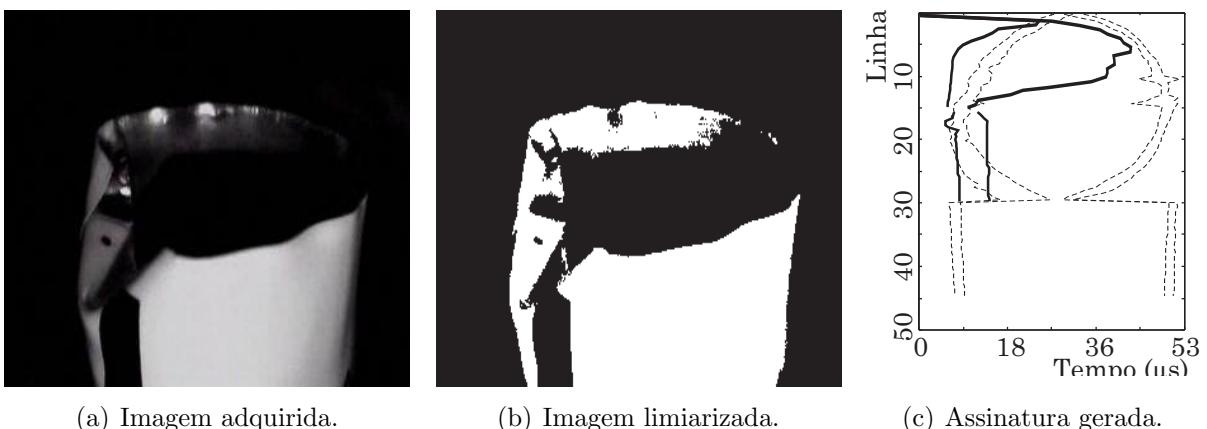

| 40 | Tubo amassado 2. O microcontrolador não detectou a região da borda inferior devido a impressão no tubo. . . . .                          | p. 86 |

|    |                                                                                                          |        |

|----|----------------------------------------------------------------------------------------------------------|--------|

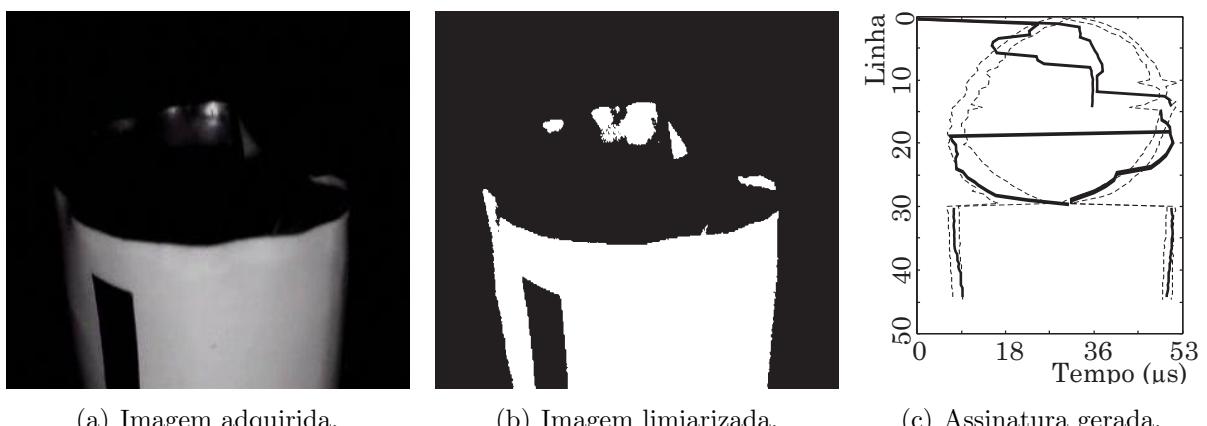

| 41 | Tubo amassado 3. Observar que a impressão não modificou a assinatura da região do corpo do tubo. . . . . | p. 86  |

| 42 | Tubo amassado 4. A pequena imperfeição modifica significantemente a assinatura. . . . .                  | p. 87  |

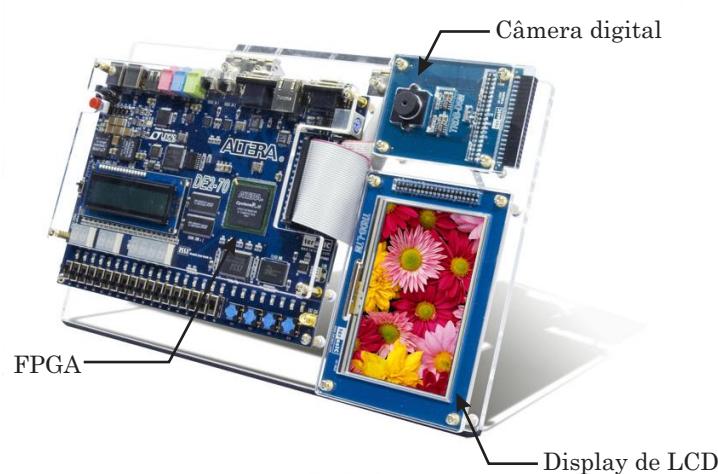

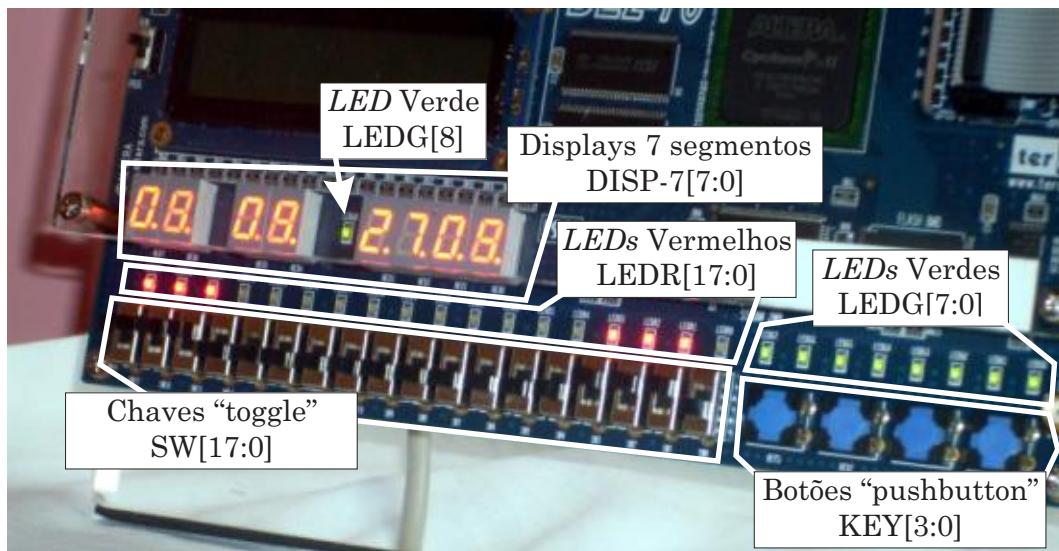

| 43 | <i>Kit</i> de desenvolvimento Altera DE2-70 para processamento de imagens. . . . .                       | p. 89  |

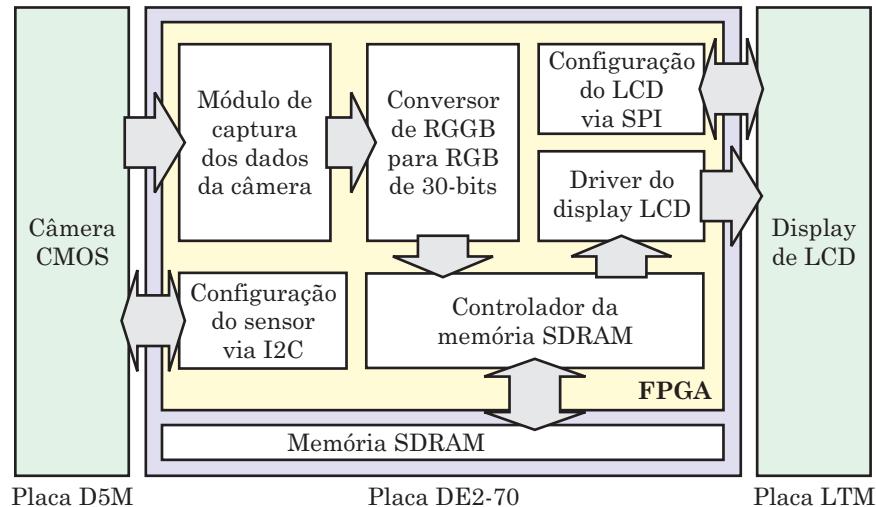

| 44 | Diagrama em blocos do exemplo. . . . .                                                                   | p. 91  |

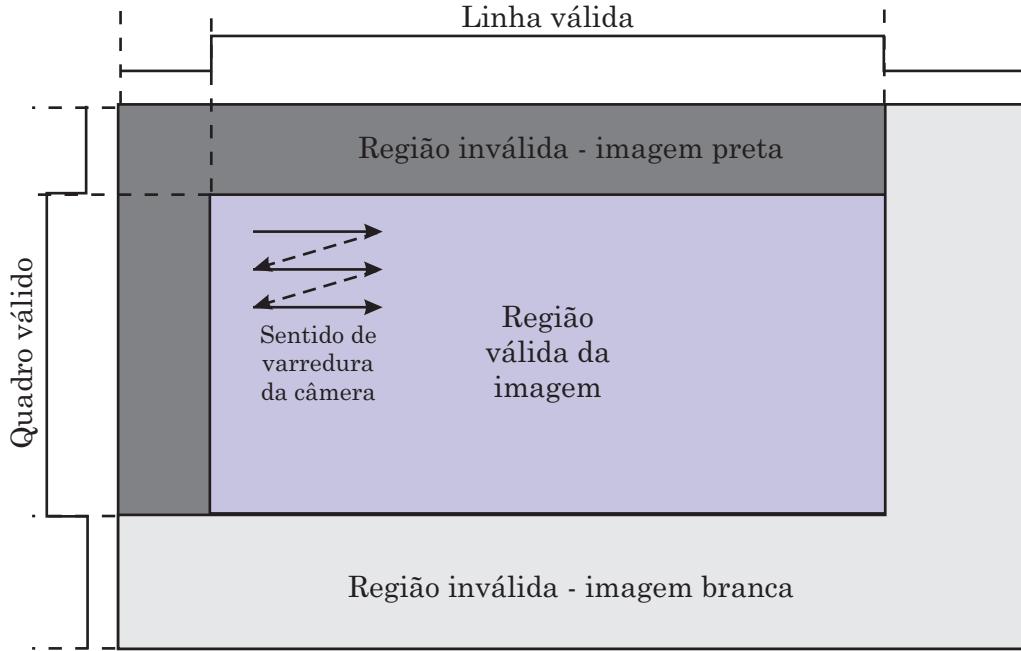

| 45 | Região válida da imagem e sinais de linha e quadro válidos. . . . .                                      | p. 93  |

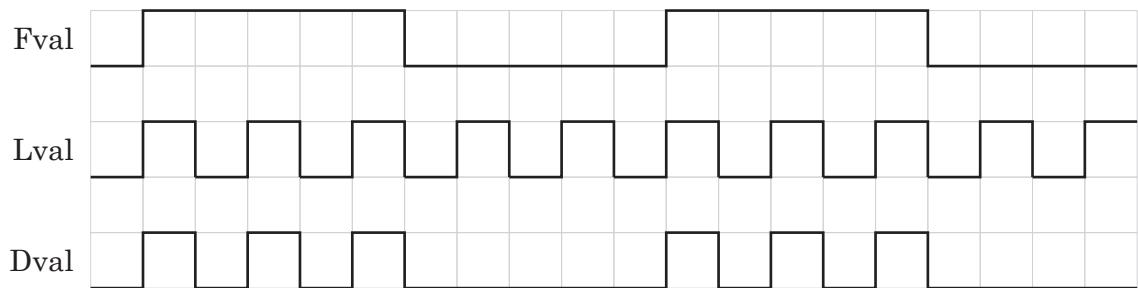

| 46 | Sinais fval, lval e dval. . . . .                                                                        | p. 93  |

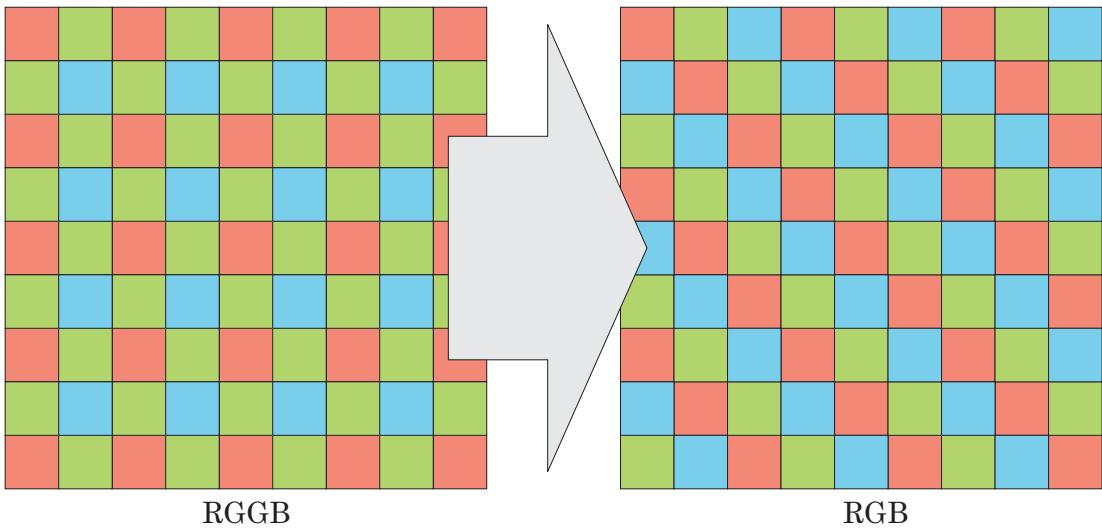

| 47 | Conversão do padrão Bayer (RGGB) para RGB. . . . .                                                       | p. 94  |

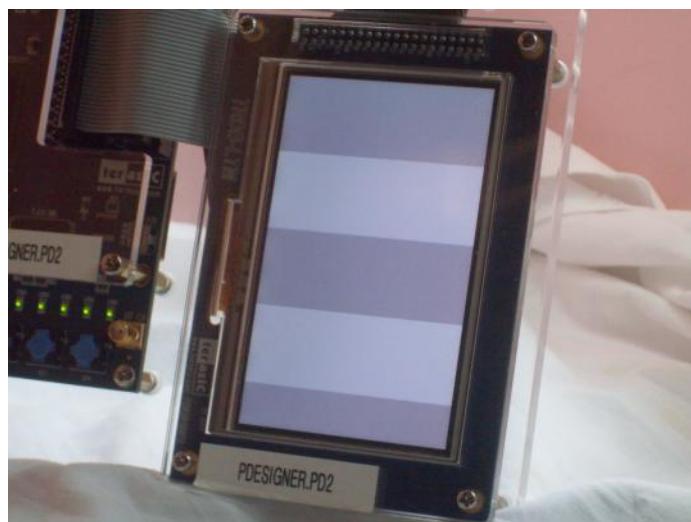

| 48 | Padrão de barras verticais gerado pela câmera e exibido no <i>display</i> de LCD do <i>kit</i> . . . . . | p. 95  |

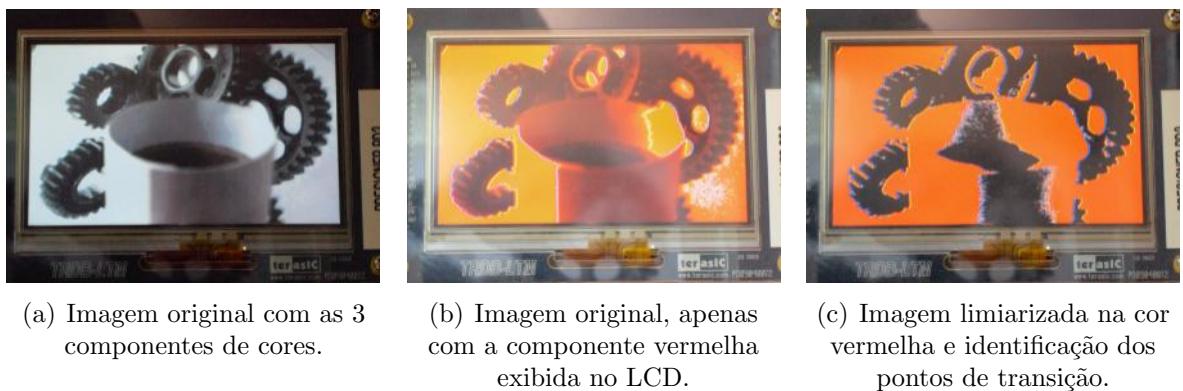

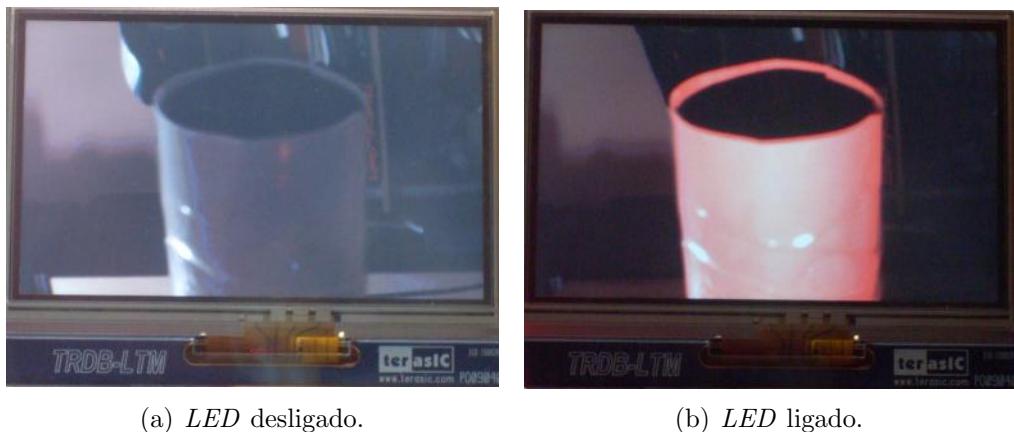

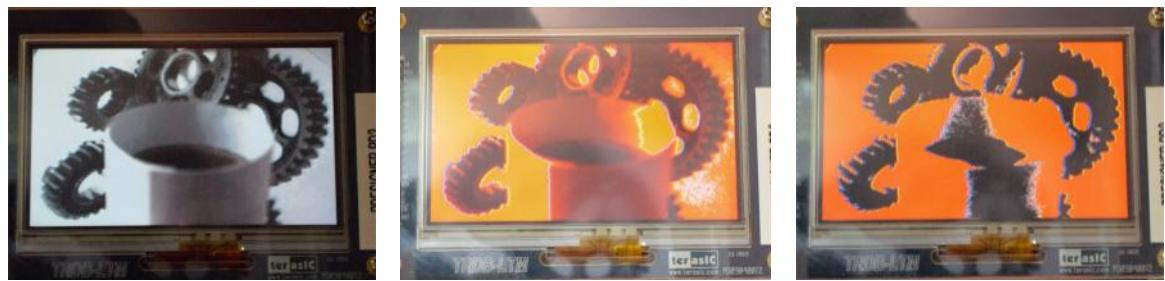

| 49 | Modos de exibição no LCD. Exemplo de exibição de um tubo com o <i>LED</i> desligado. . . . .             | p. 99  |

| 50 | Interface com o usuário da placa DE2-70. . . . .                                                         | p. 101 |

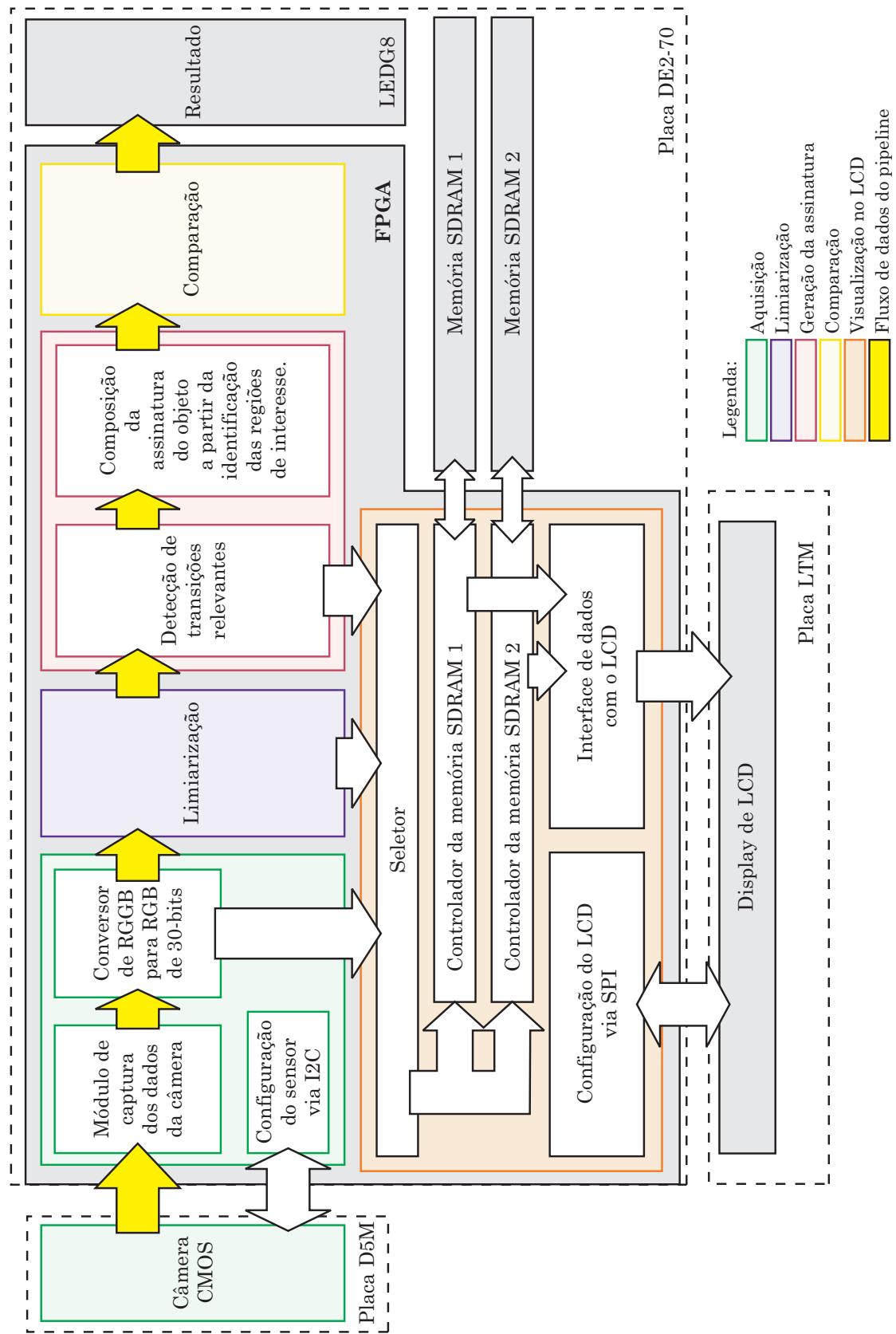

| 51 | Diagrama em blocos. . . . .                                                                              | p. 102 |

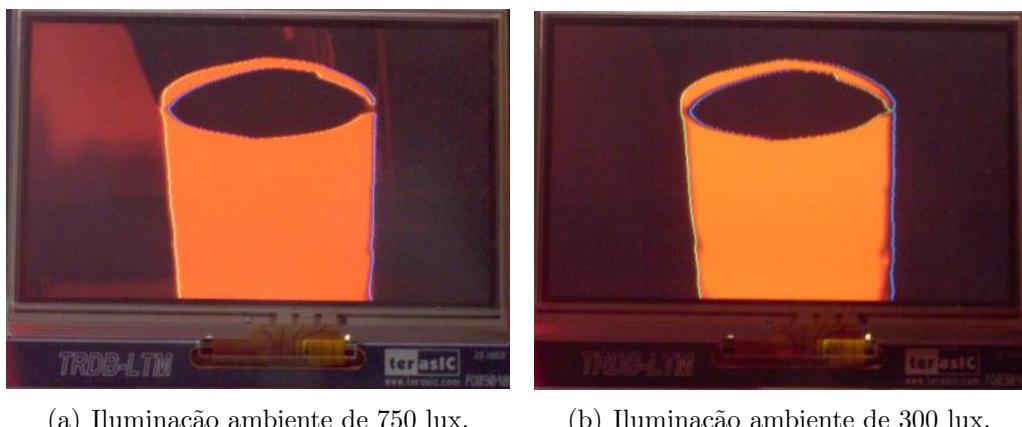

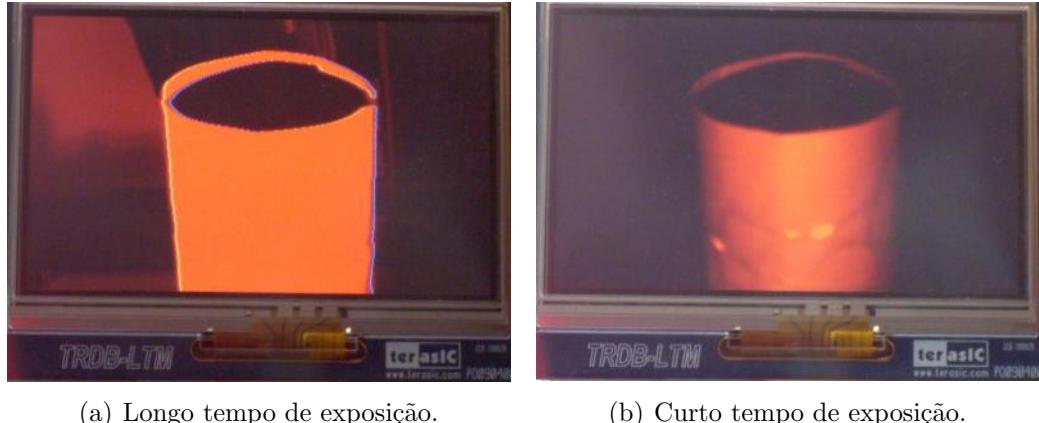

| 52 | Influência da iluminação com <i>LED</i> proposta na LEDges na aquisição da imagem. . . . .               | p. 103 |

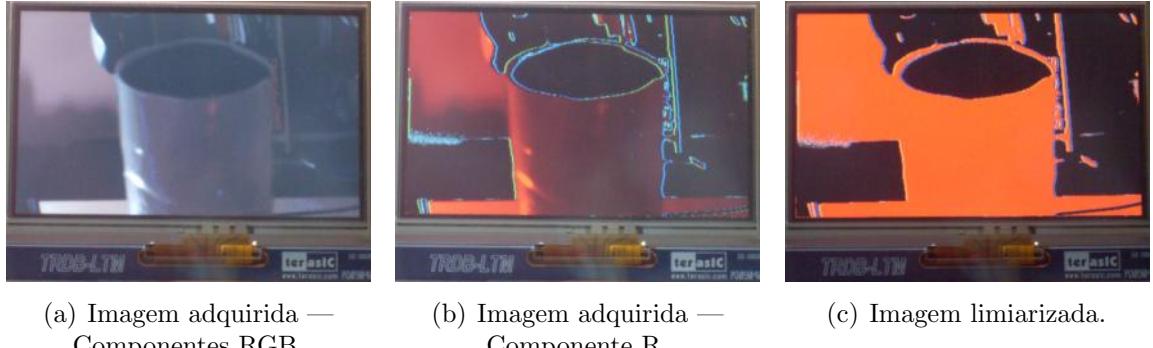

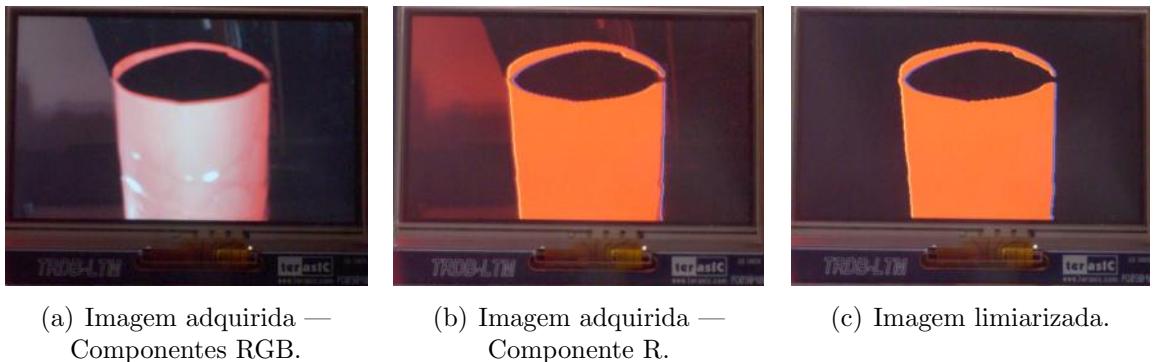

| 53 | Aquisição da imagem com as componentes RGB e somente R. . . . .                                          | p. 104 |

| 54 | Influência da iluminação ambiente na imagem adquirida. . . . .                                           | p. 104 |

| 55 | Influência do ajuste do tempo de exposição na aquisição da imagem. . . . .                               | p. 105 |

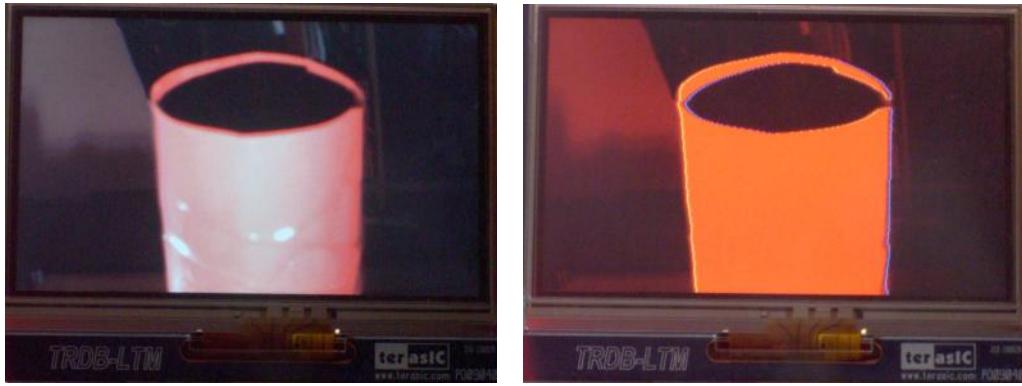

| 56 | Limiarização com o <i>LED</i> desligado. . . . .                                                         | p. 106 |

| 57 | Limiarização com o <i>LED</i> ligado. . . . .                                                            | p. 106 |

| 58 | Aparato de aquisição para testes de limiarização. . . . .                                                | p. 107 |

| 59 | Limiarização a partir da imagem adquirida com o <i>LED</i> desligado. . . . .                            | p. 107 |

| 60 | Limiarização a partir da imagem adquirida com o <i>LED</i> ligado. . . . .                               | p. 107 |

| 61 | Assinatura gerada pelo FPGA. . . . .                                                                     | p. 108 |

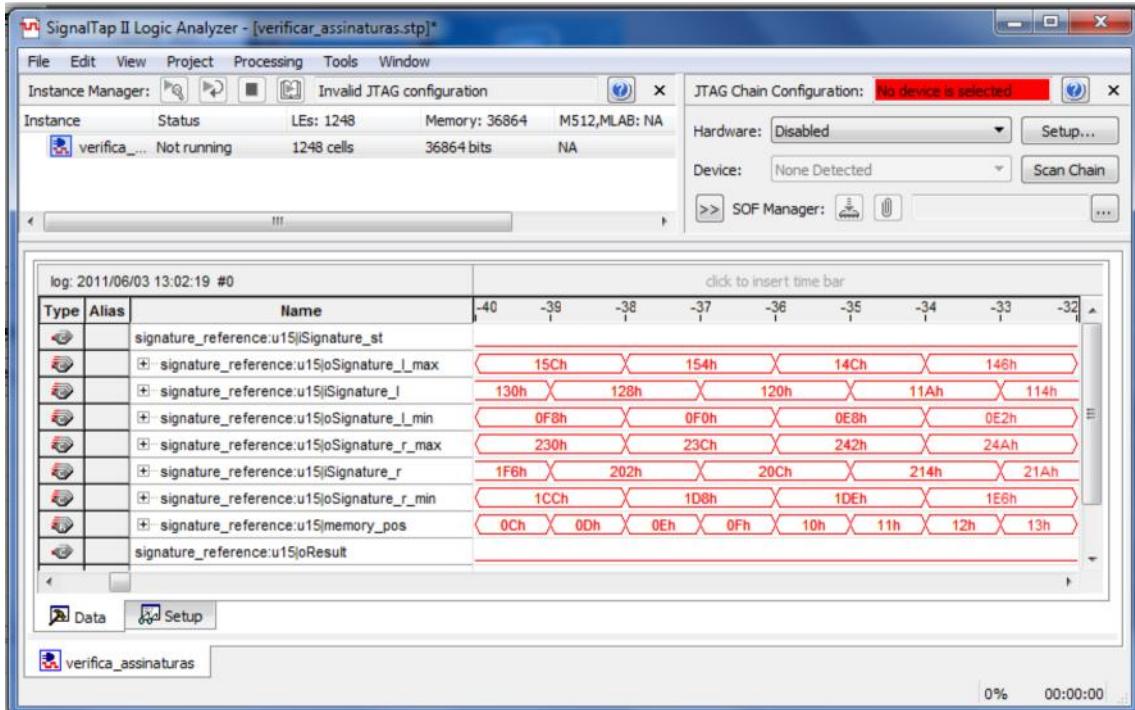

| 62 | Visualização dos dados da assinatura no Signal Tap. . . . .                                              | p. 109 |

## ***Lista de Tabelas***

|   |                                                                                                  |        |

|---|--------------------------------------------------------------------------------------------------|--------|

| 1 | Comparação entre os trabalhos relacionados com foco nas técnicas de aquisição da imagem. . . . . | p. 49  |

| 2 | Modos de exibição no <i>display</i> de LCD. . . . .                                              | p. 99  |

| 3 | Interface da LEDges com o usuário. . . . .                                                       | p. 100 |

| 4 | Utilização de recursos do FPGA na implementação da LEDges. . . .                                 | p. 110 |

| 5 | Tabela comparativa entre as técnicas de IVA. . . . .                                             | p. 114 |

| 6 | Tabela comparativa entre as implementações em microcontrolador e FPGA.p.                         | 116    |

# ***Lista de abreviaturas e siglas***

|        |                                                                                                        |       |

|--------|--------------------------------------------------------------------------------------------------------|-------|

| ASIC   | <i>Application Specific Integrated Circuit</i> - Circuito integrado para aplicação específica,         | p. 29 |

| CCD    | <i>Charge-Coupled Devices,</i>                                                                         | p. 27 |

| CMOS   | <i>Complementary MetalOxideSemiconductor,</i>                                                          | p. 28 |

| DSP    | <i>Digital Signal Processor</i> — Processador digital de sinais,                                       | p. 30 |

| FFT    | <i>Fast Fourier Transformer</i> — Transformada rápida de Fourier,                                      | p. 30 |

| FPGA   | <i>Field-programmable gate array</i> — Arranjo de portas lógicas programável,                          | p. 15 |

| IP     | <i>Intellectual Property</i> — Propriedade Intelectual,                                                | p. 30 |

| IVA    | Inspeção Visual Automática,                                                                            | p. 15 |

| LEDges | Técnica proposta nesta dissertação para deteção de irregularidades em bordas dos objetos sob inspeção, | p. 16 |

| LEs    | <i>Logic Elements</i> — Elementos Lógicos do FPGA.,                                                    | p. 86 |

| PCI    | Placa de Circuito Impressa,                                                                            | p. 33 |

| RISC   | <i>Reduced Instruction Set Computer</i> — Computador com um Conjunto Reduzido de Instruções,           | p. 30 |

| VLWI   | <i>Very Long Instruction Word</i> — Instruções com palavras muito largas,                              | p. 30 |

# *Sumário*

|          |                                                                                                                            |       |

|----------|----------------------------------------------------------------------------------------------------------------------------|-------|

| <b>1</b> | <b>Introdução</b>                                                                                                          | p. 16 |

| <b>2</b> | <b>A Inspeção Visual Automática</b>                                                                                        | p. 20 |

| 2.1      | Classificação das IVAs . . . . .                                                                                           | p. 20 |

| 2.2      | Requisitos para sistemas de inspeção visual automática . . . . .                                                           | p. 21 |

| 2.3      | Etapas de processamento da imagem em um sistema de IVA típico . . .                                                        | p. 22 |

| 2.3.1    | Processamento de baixo nível . . . . .                                                                                     | p. 23 |

| 2.3.2    | Processamento de nível intermediário . . . . .                                                                             | p. 25 |

| 2.3.3    | Processamento de alto nível . . . . .                                                                                      | p. 26 |

| 2.4      | Arquitetura típica de um sistema de IVA . . . . .                                                                          | p. 27 |

| 2.4.1    | Iluminação . . . . .                                                                                                       | p. 27 |

| 2.4.2    | Câmeras . . . . .                                                                                                          | p. 29 |

| 2.4.3    | <i>Hardware</i> específico para processamento de imagem . . . . .                                                          | p. 31 |

| 2.4.4    | Sistema computacional principal . . . . .                                                                                  | p. 33 |

| 2.4.5    | Sistema de controle, sensores e atuadores do processo produtivo                                                            | p. 34 |

| 2.5      | Exemplos de IVA dimensional . . . . .                                                                                      | p. 34 |

| 2.6      | Análise do capítulo . . . . .                                                                                              | p. 36 |

| <b>3</b> | <b>Trabalhos relacionados</b>                                                                                              | p. 38 |

| 3.1      | Técnicas de aquisição da imagem visando segmentação dos objetos no primeiro plano e identificação de suas bordas . . . . . | p. 38 |

| 3.1.1    | Extração do primeiro plano a partir de pares de imagens, com e sem iluminação específica no objeto . . . . .               | p. 39 |

|          |                                                                                                  |       |

|----------|--------------------------------------------------------------------------------------------------|-------|

| 3.1.2    | Iluminação com luz infra-vermelha para identificação do primeiro plano . . . . .                 | p. 40 |

| 3.1.3    | Utilização de câmeras com registro de profundidade . . . . .                                     | p. 42 |

| 3.1.4    | Detecção do primeiro plano em imagens com plano de fundo estático                                | p. 43 |

| 3.1.5    | Utilização de iluminação a <i>laser</i> . . . . .                                                | p. 43 |

| 3.1.6    | Inspeção de objetos baseado em iluminação estruturada a partir de projetores de padrão . . . . . | p. 45 |

| 3.2      | Técnicas para segmentação da imagem a partir da descontinuidade . .                              | p. 45 |

| 3.2.1    | Detecção da borda a partir do gradiente da imagem . . . . .                                      | p. 46 |

| 3.3      | Implementação da IVA em sistemas embarcados . . . . .                                            | p. 47 |

| 3.4      | Análise do capítulo . . . . .                                                                    | p. 48 |

| <b>4</b> | <b>LEDges: uma técnica de IVA baseada em limiarização da imagem e geração de assinaturas</b>     | p. 51 |

| 4.1      | Aquisição da imagem . . . . .                                                                    | p. 53 |

| 4.2      | Limiarização . . . . .                                                                           | p. 56 |

| 4.3      | Geração da assinatura . . . . .                                                                  | p. 58 |

| 4.4      | Comparação . . . . .                                                                             | p. 61 |

| 4.5      | Restrições para aplicação da LEDges . . . . .                                                    | p. 63 |

| 4.6      | Análise do capítulo . . . . .                                                                    | p. 64 |

| <b>5</b> | <b>Avaliação de arquiteturas para implementação</b>                                              | p. 66 |

| 5.1      | Análise da técnica . . . . .                                                                     | p. 67 |

| 5.2      | Modelagem da LEDges em computador . . . . .                                                      | p. 68 |

| 5.3      | Otimização . . . . .                                                                             | p. 72 |

| 5.4      | Escolha do processador . . . . .                                                                 | p. 73 |

| 5.5      | Análise do capítulo . . . . .                                                                    | p. 76 |

| <b>6</b> | <b>Arquitetura baseada em microcontrolador e câmera analógica</b>                                | p. 78 |

|          |                                                                              |        |

|----------|------------------------------------------------------------------------------|--------|

| 6.1      | Diagrama em blocos . . . . .                                                 | p. 78  |

| 6.2      | Estudo de caso: detecção de amassados em tubos de creme dental . . .         | p. 80  |

| 6.2.1    | Aquisição da imagem . . . . .                                                | p. 80  |

| 6.2.2    | Limiarização . . . . .                                                       | p. 81  |

| 6.2.3    | Geração da assinatura . . . . .                                              | p. 83  |

| 6.2.4    | Comparação . . . . .                                                         | p. 84  |

| 6.3      | Análise do capítulo . . . . .                                                | p. 87  |

| <b>7</b> | <b>Arquitetura baseada em FPGA e câmera digital</b>                          | p. 88  |

| 7.1      | <i>Kit Altera DE2-70</i> . . . . .                                           | p. 88  |

| 7.1.1    | <i>Design</i> inicial para aplicações com câmera e <i>display</i> de LCD . . | p. 90  |

| 7.2      | Blocos funcionais da implementação da LEDges em FPGA . . . . .               | p. 92  |

| 7.2.1    | Aquisição da imagem . . . . .                                                | p. 92  |

| 7.2.2    | Limiarização . . . . .                                                       | p. 95  |

| 7.2.3    | Geração da assinatura . . . . .                                              | p. 96  |

| 7.2.4    | Comparação . . . . .                                                         | p. 97  |

| 7.2.5    | Visualização no LCD . . . . .                                                | p. 98  |

| 7.2.6    | Módulo de <i>reset</i> . . . . .                                             | p. 99  |

| 7.2.7    | Interface com o usuário . . . . .                                            | p. 100 |

| 7.2.8    | Diagrama em blocos . . . . .                                                 | p. 100 |

| 7.3      | Estudo de caso: detecção de amassados em tubos de creme dental . .           | p. 101 |

| 7.3.1    | Aquisição da imagem . . . . .                                                | p. 101 |

| 7.3.2    | Limiarização . . . . .                                                       | p. 105 |

| 7.3.3    | Geração da assinatura . . . . .                                              | p. 108 |

| 7.3.4    | Comparação . . . . .                                                         | p. 108 |

| 7.3.5    | Relatório de implementação . . . . .                                         | p. 109 |

| 7.4      | Análise do capítulo . . . . .                                                | p. 110 |

|                                                 |        |

|-------------------------------------------------|--------|

| <b>8 Resultados</b>                             | p. 113 |

| <b>9 Conclusões e trabalhos futuros</b>         | p. 117 |

| <b>Referências</b>                              | p. 120 |

| <b>Apêndice A – Modelagem em FreeMat</b>        | p. 123 |

| <b>Apêndice B – Código em “C” para ARM7</b>     | p. 126 |

| <b>Apêndice C – Código em Verilog para FPGA</b> | p. 134 |

# 1 *Introdução*

Apesar da maturidade dos processos industriais, falhas podem ocorrer e gerar defeitos nos produtos resultantes da produção industrial. Como exemplo, observamos a produção em série de partes mecânicas, popularizada após a segunda fase da revolução industrial, no início do século XIX. Neste caso é comum que os erros no processo produtivo impactem nas dimensões do objeto em processamento e precisem ser identificados antes da entrega deste produto para ser utilizado, seja como parte integrante de um sistema maior ou seja este já o produto final.

Como exemplo será apresentado um caso industrial real, observado na filial de uma empresa multinacional instalada no município do Cabo de Santo Agostinho, Pernambuco. O transporte inapropriado de tubos vazios de creme dental pode gerar leves amassamentos nestes tubos. E, se a irregularidade não for detectada a tempo, a injeção do creme dental no tubo amassado falhará e o creme transbordará, gerando parada imediata de todo o processo produtivo. Neste caso, a parada dura aproximadamente dez minutos para manutenção da injetora e esta falha ocorre com uma freqüência aproximada de duas vezes por dia.

Tradicionalmente, a inspeção visual é realizada por pessoas, geralmente especialistas (2). Apesar de pessoas terem a capacidade de realizar a maior parte destes trabalhos melhor que as máquinas, os humanos são mais lentos e a baixa frequência das falhas torna a inspeção uma tarefa enfadonha. Como consequência, pode ser necessária a mobilização de um grande número de recursos humanos para executar a inspeção. Além disto, profissionais especialistas são difíceis de encontrar no mercado e, quando contratados, de se manter na indústria. Adicionalmente, para formar bons profissionais é necessário fornecer treinamentos e as suas habilidades são desenvolvidas lentamente ao longo do tempo. Associado a estas dificuldades, existem casos onde a inspeção é tediosa ou difícil, mesmo para os melhores profissionais. Em algumas aplicações as informações devem ser rapidamente ou repetitivamente extraídas do cenário. Por exemplo, a inspeção de parafusos em trilhos de trem, com este em movimento a 200 km/h (3), e a detecção de irregularidades

em bocas de garrafas em uma linha de produção de 30.000 garrafas por hora (4) são tarefas impossíveis para um humano. Por fim, há ainda os casos onde a inspeção humana pode ser uma atividade perigosa ou o local do objeto a ser inspecionado pode ser de difícil acesso; por exemplo, em reatores nucleares, na indústria química e farmoquímica, em fornos industriais, no fundo do oceano, etc. Nestes casos, proibitivos para a inspeção humana, máquinas podem ser utilizadas para realizar as inspeções visuais necessárias.

A Inspeção Visual Automática (IVA) é uma das principais aplicações de visão de máquina<sup>1</sup>. Além de possibilitar inspeções complexas, em ambientes perigosos ou de difícil acesso, a inspeção visual automática também pode melhorar a produtividade e a qualidade nas linhas de produção industriais (6). Por exemplo, o sistema de IVA implementado por Fernandez et al.(7) analisa a classificação de gomos de laranjas. Foram definidos dois tipos de erros de classificação: o tipo I, gomos bons classificados como ruins, e o tipo II, gomos ruins classificados como bons. Não houve benefícios significativos na precisão da classificação relacionada aos erros tipo I. Para estes erros, a inspeção humana falha em 18% das amostras enquanto a inspeção automática falha em 14,6% das amostras (redução dos erros em 19%). O ganho significativo na precisão foi obtido em relação aos erros tipo II. Neste caso, a inspeção humana falha em 30% das amostras enquanto a inspeção automática falha em 10,4% destas (redução dos erros em 65%). Além da precisão, a velocidade da inspeção também houve ganhos significativos. O sistema automático foi implementado em duas arquiteturas: uma utiliza como unidade de processamento um Pentium III e, a segunda, utiliza um FPGA. A inspeção humana necessita de 600 ms/- gomo enquanto a inspeção automática precisa de apenas 64 ms/gomo ou 22 ms/gomo se utilizada a arquitetura com o Pentium III ou com o FPGA respectivamente. Neste caso, observa-se que as inspeções com FPGA são 27 vezes mais rápidas que a inspeção humana.

Em particular, dentre os diferentes tipos de IVA, um de grande importância e constantemente demandado pela indústria, é o tipo dimensional (6). Por exemplo, o sistema de IVA implementado por Duan et al.(4) identifica o diâmetro e centro das garrafas produzidas. Outros exemplos são a análise da qualidade da soldagem em PCB (8), a medição de dimensões de cones de auto-falantes (9) e identificação de irregularidades nas bordas de tubos. Este último será implementado neste trabalho de mestrado. Como pode ser observado, existe uma ampla gama de aplicações para a IVA, sendo que cada aplicação apresenta diferentes requisitos, principalmente de desempenho, taxa de acertos da classificação para os objetos inspecionados, portabilidade, eficiência energética e custo da solução.

---

1. Ramo da engenharia que usa visão computacional no contexto da manufatura. (5)

Apesar da relevância da IVA para a automação industrial, ainda existem alguns desafios que precisam ser resolvidos. Sistemas de IVA são, geralmente, baseados em soluções complexas, como por exemplo, redes neurais (4, 8) e transformadas de Hough (10, 11). Estas soluções requerem uma ampla capacidade de processamento e de armazenamento, sendo implementadas, normalmente, em computadores industriais (4, 8, 9).

Outro aspecto importante que influencia significantemente na complexidade do sistema, sobretudo no algoritmo necessário para realizar o processamento da imagem, são as técnicas de aquisição da imagem, incluindo o tipo de iluminação utilizado. Geralmente são utilizados iluminação com laser (9, 10), projetores de padrões (12, 13) e multiplexação na iluminação difusa (8, 14). Esta complexidade impacta, principalmente, no custo e no desempenho das soluções existentes no mercado, tornando estas proibitivas para certas aplicações onde é necessário obter elevadas taxas de inspeção ou reduzir custos do equipamento de inspeção.

Neste trabalho é descrita uma nova técnica para inspeção visual automática dimensional para aplicações de tempo real, LEDges. As contribuições desta técnica são:

1. Uso de uma nova estratégia para iluminação, baseada em LEDs de alta potência, que torna mais fácil a identificação das bordas de interesse;

2. Algoritmo muito simples e eficiente para realizar a segmentação, representação e descrição da imagem;

3. Uso reduzido de memória para realizar todo o processamento da imagem;

4. Eliminação da necessidade de capturar o quadro inteiro antes de realizar a inspeção nas bordas de interesse.

Também são avaliadas neste trabalho duas possibilidades de arquitetura para implementar a LEDges em sistema embarcado de baixa capacidade computacional, particularmente em termos de memória e processador. Estas possibilidades foram pesquisadas e pensadas a fim de resolver um problema industrial real de IVA onde é necessário detectar amassamentos em bordas de tubos de creme dental, em linha de produção industrial.

Pelas pesquisas realizadas, não existe uma solução de IVA disponível no mercado que atenda a todos estes requisitos. Com o objetivo de preencher esta lacuna tecnológica e validar a técnica proposta, após análise das possíveis arquiteturas, a LEDges foi implementada em duas configurações, baseadas em:

1. Microcontrolador e câmera analógica;

## 2. FPGA e câmera digital.

Foram medidos alguns parâmetros e comparados com outros trabalhos relacionados que utilizam diferentes técnicas e infra-estruturas em relação àquelas desenvolvidas neste trabalho. Estas comparações não são triviais uma vez que cada trabalho tem seus requisitos específicos. Porém, pode-se observar que, de um modo geral, as implementações realizadas neste trabalho obtiveram melhores taxas de inspeção em relação às obtidas pelos outros trabalhos relacionados com infra-estrutura semelhante.

Esta dissertação está estruturada conforme descrito a seguir: No capítulo 2 é contextualizada a IVA dimensional. Os trabalhos relacionados são analisados no capítulo 3. A técnica proposta, LEDges, é apresentada no capítulo 4. Uma avaliação das possíveis arquiteturas para implementação da técnica proposta pode ser vista no capítulo 5. Nos capítulos 6 e 7 são apresentadas duas implementações da técnica: a primeira baseada em microcontrolador e câmera analógica e, a segunda, baseada em FPGA e câmera digital. Por fim, os resultados são apresentados no capítulo 8 e as conclusões no capítulo 9.

## 2 A Inspeção Visual Automática

Neste capítulo serão abordados os tipos de inspeção visual automática e os requisitos para implementação de um sistema de IVA. Além disto, serão apresentadas as etapas do processamento da imagem em um sistema de IVA típico, além da arquitetura básica utilizada em sistemas deste tipo. Este capítulo se encerra com alguns exemplos de IVA dimensional.

### 2.1 Classificação das IVAs

Em sistemas de visão industrial, é possível classificar as inspeções em quatro tipos básicos: superficial, estrutural, operacional e dimensional (6). Na inspeção da qualidade superficial são analisados texturas, arranhões, rachaduras, grau de rugosidade, continuidade, etc. Um exemplo típico de aplicação é a análise da qualidade de carne de aves baseada na cor da amostra (15). O segundo tipo, a inspeção da qualidade estrutural, analisa a montagem de partes mecânicas em um produto maior, verificando o posicionamento de furos, cortes, rebites, parafusos e a presença de objetos estranhos. Por exemplo, na verificação da montagem de portas e janelas em automóveis na linha de produção (16). O terceiro tipo de inspeção, a de qualidade operacional, analisa a incompatibilidade das operações aos padrões e especificações técnicas. Um exemplo desta inspeção é a verificação do processo de soldagem a *laser* (17). Por fim, a inspeção da qualidade dimensional está relacionada com a inspeção de dimensões, formas, posição, orientação, alinhamento. Este tipo de inspeção é o objeto principal desta dissertação.

Checkar se as dimensões de um objeto estão dentro das tolerâncias especificadas ou se os objetos tem a forma correta, são tarefas comuns nas indústrias (6). Tais tarefas envolvem a inspeção de características geométricas do objeto, em duas ou três dimensões, e são denominados inspeção da qualidade dimensional, ou, simplesmente, inspeção dimensional. Várias indústrias estão envolvidas no desenvolvimento de sistemas de visão para automatizar a medição da qualidade dimensional. As tarefas variam desde verificar o nível

de um líquido na garrafa em indústrias de embalagens, até verificar e transmitir pela internet em tempo real a concentricidade e o diâmetro de bombas de *airbags* em carros. Um exemplo de IVA dimensional em tempo real pode ser visto em (18). Nesta aplicação são comparados produtos impressos em alta resolução, com alto grau de similaridade, onde a detecção de diferenças mínimas torna este trabalho bastante difícil para os humanos, principalmente quando este deve ser realizado em tempo real.

## 2.2 Requisitos para sistemas de inspeção visual automática

Existe uma ampla gama de aplicações para a IVA. Para cada domínio de aplicações existem diferentes requisitos, tais como a taxa de inspeção, a informação relevante na cena que deve ser analisada, a precisão, a portabilidade, o consumo energético, os recursos computacionais necessários, o tipo do sinal de saída do sistema, etc. As diferenças nos requisitos existem uma vez que características do ambiente e da resposta esperada pelo sistema também são diferentes, tais como a iluminação local, objeto a ser inspecionado, velocidade da produção, características que precisam ser analisadas no objeto (tipo de inspeção), infra-estrutura pré-existente para realizar a interface com o usuário (ex.: redes e controladores industriais), a ação desejada como resposta, etc. Por exemplo, em algumas aplicações, o sistema deve ser capaz de diferenciar objetos com variações aceitáveis nas medidas dimensionais daqueles com variações inaceitáveis, enquanto em outras aplicações, o sistema deve ser capaz de identificar problemas de alinhamento em montagem de partes mecânicas. Logo, não existem sistemas de visão industrial capazes de abranger todas as tarefas, em todos os campos de aplicação.

O primeiro problema a resolver para automatizar as tarefas de inspeção visual é identificar que tipo de informações a máquina busca e como traduzir estas informações em medições ou características extraídas das imagens. Por exemplo, é importante especificar o que “defeito” significa em termos de medições e regras. Somente então é possível implementar estas atividades em *software* ou *hardware* (6). São comuns nas indústrias aplicações que visam simplesmente classificar o objeto sob inspeção entre “bom” e “ruim” <sup>1</sup>.

Para que o sistema seja confiável, este deve reduzir o máximo possível os “*escape rates*”, que são os casos inaceitáveis detectados como aceitáveis, e os “*false alarms*”, que

---

1. Na IVA dimensional, objeto “bom” é aquele que tem valores de seus parâmetros dimensionais de acordo com os padrões estabelecidos pela indústria. Analogamente, objeto “ruim” é aquele que tem seus parâmetros desconformes com os padrões estabelecidos.

são os casos aceitáveis detectados como inaceitáveis. É responsabilidade das unidades de processamento manter o sistema confiável, sendo que a eficiência da classificação depende também da qualidade da imagem adquirida. Além de confiável, o sistema de visão industrial também deve ser robusto. Isto é, deve ser capaz de se adaptar a variações na iluminação, a marcas no objeto e realizar a inspeção mesmo com o objeto em posições incertas, sem perder a precisão e o desempenho. Além disto, o sistema de IVA deve ser capaz de identificar o objeto sob inspeção, mesmo que o plano de fundo seja composto por outros objetos com diversas formas, texturas e iluminação. Altos níveis de robustez são muito difíceis de obter ou, pelo menos, requerem um uso muito intenso de recursos computacionais. Logo, é desejável que o processo industrial possua o mínimo de incertezas nos parâmetros relacionados com o ambiente da inspeção.

Um sistema de visão industrial deve ser rápido e eficiente no custo (6) e, inclusive, possibilitar rápidas taxas de inspeção mesmo sem uso de câmeras de alta velocidade. Finalmente, um sistema de IVA deve permitir a sua instalação em espaço físico restrito. Nem sempre é possível realizar a montagem da nova solução de IVA na infra-estrutura de produção pré-existente.

Desta forma, existe uma demanda crescente por sistemas de IVA embarcados visando atender às aplicações que necessitam melhores índices de desempenho e otimizar o uso de recursos computacionais, como observado em (3, 7, 19).

### **2.3 Etapas de processamento da imagem em um sistema de IVA típico**

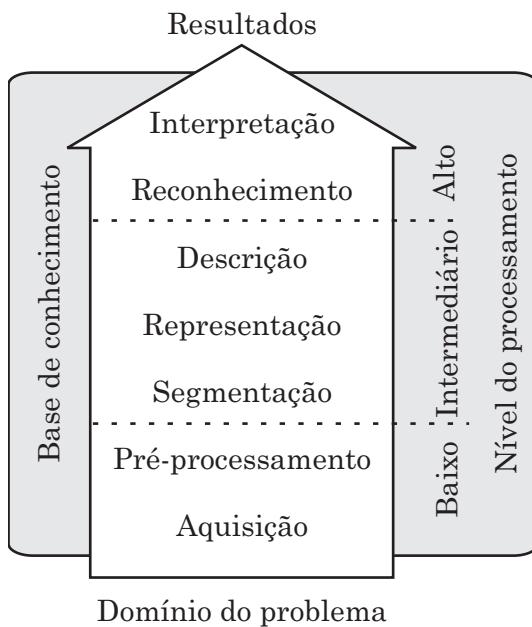

A Fig. 1 mostra as etapas do processamento de imagens em um sistema de IVA típico. Estas etapas podem ser divididas em três níveis distintos de processamento. O primeiro nível, processamento de baixo nível, trata da aquisição da imagem e o melhoramento da qualidade desta. O nível intermediário resulta na descrição da imagem em um conjunto numérico digital capaz de ser processado por um sistema computacional. Por fim, o processamento de alto nível é responsável pelo reconhecimento da imagem e, finalmente, sua interpretação indicando se o objeto sob inspeção está, ou não, dentro dos padrões aceitáveis pela indústria.

A “base de conhecimento” contém uma base de dados e conhecimentos acumulados sobre a inspeção, pelo homem ou pela máquina. A interação com a base de conhecimento em todas as etapas é essencial para tornar mais precisas as tomadas de decisão, e deve

ser vista como parte integrante do processamento da imagem (20).

Parte dos conhecimentos acumulados podem ser experiências da equipe em relação a uma inspeção manual que será automatizada, onde já são conhecidos os resultados relacionados aos problemas e suas soluções. Por exemplo, na seleção manual de uma região da imagem aonde está o objeto que será inspecionado. Outro exemplo de banco de conhecimento é um banco de dados contendo todas as especificações de uma indústria para a fabricação de um produto. Estes dados serão consultados pelo computador e, se os parâmetros adquiridos durante a IVA não estiverem de acordo com os valores registrados no banco de dados, o objeto sob inspeção será classificado como “ruim”.

Figura 1: Etapas de processamento de um sistema de IVA típico.

### 2.3.1 Processamento de baixo nível

O primeiro nível de processamento, o “baixo nível”, é dividido em duas etapas: (i) aquisição da imagem e (ii) pré-processamento.

#### Aquisição da imagem

A etapa de aquisição da imagem consiste em capturar e transferir a imagem de uma câmera, *scanner* ou arquivo salvo em uma unidade de armazenamento para a unidade de processamento. No caso da IVA em tempo real, os dispositivos de captura da imagem são uma ou mais câmeras, sendo que algumas destas câmeras podem ser configuradas para capturar apenas a região de interesse e para ajustar o tempo de exposição.

É possível aumentar a velocidade da inspeção a partir da escolha da região de interesse,

quando áreas periféricas da imagem, sem informações relevantes para a inspeção, são excluídas. Isto se dá uma vez que o algoritmo de processamento poderá ser executado em um menor número de pixels. Além disto, é possível melhorar a taxa de acertos da inspeção se uma área de difícil segmentação puder ser excluída nesta etapa do processamento. A segmentação da imagem será tratada na seção 2.3.2.

Quanto ao tempo de exposição, este é fundamental na determinação do tempo total da IVA. Quanto mais rápida for a exposição, mais rápida será a aquisição da imagem, porém, menos luz será captada pelo sensor. Logo, para aumentar a velocidade da aquisição através da redução do tempo de exposição, é necessário iluminar vigorosamente o objeto sob inspeção. Adicionalmente, se a iluminação for estruturada de modo a iluminar somente a região relevante do objeto sob inspeção, é possível ainda que a redução no tempo de exposição reduza o esforço computacional para realizar a segmentação da imagem uma vez que as informações irrelevantes do objeto e do plano de fundo não serão captadas pelo sensor.

### **Pré-processamento**

A segunda etapa do processamento de baixo nível é o pré-processamento da imagem. Esta etapa visa melhorar a qualidade da imagem através da redução de ruídos e distorções, além do ajuste de brilho e contraste. Com isto é possível reduzir os esforços computacionais para extrair as características relevantes da imagem para a IVA. Por exemplo, o pré-processamento pode ser realizado através de um filtro mediano para reduzir os ruídos impulsivos, implementado em FPGA (21). As tarefas do pré-processamento podem ser realizadas na própria câmera, em um *hardware* específico para processamento de imagens, ou no sistema computacional principal. O *hardware* no qual será implementado o pré-processamento depende dos requisitos de desempenho do sistema.

Quando não é exigido um elevado desempenho, o pré-processamento poderá ser realizado somente no sistema computacional principal, que é para uso geral, como realizado na inspeção de garrafas apresentado em (4). Porém, quando é exigido um elevado desempenho, sobretudo em aplicações em tempo real, o pré-processamento deve ser realizado na câmera, para ajuste de brilho e contraste ou em um *hardware* específico, para a redução de ruídos e distorções. Um exemplo desta arquitetura está no sistema de IVA implementado por Fernandez et al.(7) que analisa a classificação de gomos de laranjas.

### 2.3.2 Processamento de nível intermediário

O nível intermediário de processamento é composto pelas etapas de: (i) segmentação, (ii) representação e (iii) descrição da imagem.

#### Segmentação

A segmentação, que identifica as regiões de interesse, pode ser uma das atividades mais complexas do processamento da imagem. Por um lado, um procedimento de segmentação robusto favorece substancialmente a solução bem sucedida de um problema de processamento de imagens. Por outro lado, algoritmos de segmentação inadequados quase sempre geram falha no processamento.

Tipicamente o algoritmo de segmentação visa localizar regiões e formas específicas nas imagens. O resultado é um conjunto de regiões ou um conjunto de contornos (bordas) extraídos da imagem. Por exemplo, no caso de reconhecimento de caracteres, o papel básico da segmentação é extrair caracteres individuais e palavras do fundo da imagem. A segmentação pode ser baseada em formatos, tal como na detecção de descontinuidades, pontos, linhas e bordas, ou pode ser baseada nas características dos pixels, tal como cores e intensidades.

Vários algoritmos e técnicas específicas de segmentação foram desenvolvidos, não havendo, porém, uma solução geral para o problema de segmentação de imagens. Muitas vezes para a resolução de um problema de segmentação de imagem é necessário a combinação de técnicas visando sua adaptação ao domínio do problema.

#### Representação

Em seguida, a imagem é representada em termos de suas características internas (pixels que compõem a região) ou externas (bordas). De um modo geral, a representação pela borda é adequada quando o interesse se concentra nas características da forma externa, tais como cantos ou pontos de inflexão. A representação por região é adequada quando o interesse se concentra em propriedades internas, tais como textura ou a forma do esqueleto. Por exemplo, a representação baseadas nos pixels que compõe a região pode ser observada em (22), inclusive a utilização de um limiar para “binarização” da imagem pode ser observada em (10, 23). A representação pelas bordas é mostrado em (4, 8).

#### Descrição

A próxima etapa consiste em descrever a região de interesse com base na representação escolhida. Por exemplo, a região pode ser representada por suas bordas e descrita pelo

tamanho ou número de concavidades nesta borda. Assim como nas etapas anteriores, o principal objetivo é fazer com que as características de interesse sejam enfatizadas.

Um exemplo de descrição é o conjunto de assinaturas gerado em (9), inspeção de cones de alto-falantes, quando a altura do cone é descrita por um conjunto de medidas de distância entre a base da mesa e o topo do cone.

O processamento de nível intermediário é realizado no sistema computacional principal, de uso geral, ou, quando necessário um desempenho superior, em um *hardware* específico. No caso de utilizar um *hardware* específico, é importante pesquisar os modelos que disponibilizam um pacote de *software* integrado ao hardware. Por exemplo, o Sherlock, da Teledyne Dalsa<sup>2</sup>, é um pacote *software* baseado em Windows que se integra à plataforma MVTools. Estas ferramentas possuem 204 funções de visão computacional. Alguns algoritmos disponíveis são de geração de padrão, convolução, detecção de bordas, transformada de Fourier, transformações geométricas, entre outras.

### 2.3.3 Processamento de alto nível

O processamento de alto nível é composto pelo reconhecimento e interpretação da imagem.

#### Reconhecimento

O reconhecimento de padrões é a primeira etapa do processamento em alto nível. O reconhecimento consiste basicamente na classificação da descrição do objeto. Por exemplo, na leitura automática de um texto impresso, os padrões de interesse são os caracteres alfanuméricos. A meta é atingir uma dada precisão de reconhecimento de caracteres que sejam a mais próxima possível à excelente capacidade exibida por seres humanos na realização de tais tarefas.

#### Interpretação

A última etapa da IVA é a interpretação da imagem, que consiste em atribuir um significado aos diversos elementos reconhecidos na imagem.

Ao final do processamento de alto nível o sistema será capaz de tomar decisões, como controlar um processo produtivo (por exemplo, guiando um braço robótico), propagar características para outras etapas do processo (por exemplo, separação de tipos diferentes de peças) e detectar defeitos ou falhas (por exemplo, descartando peças quebradas).

---

2. <http://www.teledynedalsa.com/>

Em geral, os algoritmos para reconhecimento e interpretação da imagem são executados nos sistemas computacionais principais, de uso geral. Porém, nos casos em que é necessário maior desempenho, podem ser utilizados *hardwares* específicos que descrevem a rede neural ou lógica fuzzy, como o W.A.R.P., da SGS-Thomson<sup>3</sup>. Este é projetado para acelerar aplicações fuzzy. Para desenvolvimento de redes neurais, por exemplo, há o Trajan 6.0, da Trajan software<sup>4</sup>. Este software permite a construção de redes híbridas, *perceptrons* multicamadas, Kohonen, pseudo-Newton, entre outros. A saída deste software gera como resultado um código fonte em C ou um API de C/C++, Visual Basic, Excel, etc. É importante sempre verificar se a plataforma de *hardware* que será adquirida tem pacotes de *software* que permitem uma descrição em alto nível da rede neural ou lógica fuzzy para geração de um código otimizado.

## 2.4 Arquitetura típica de um sistema de IVA

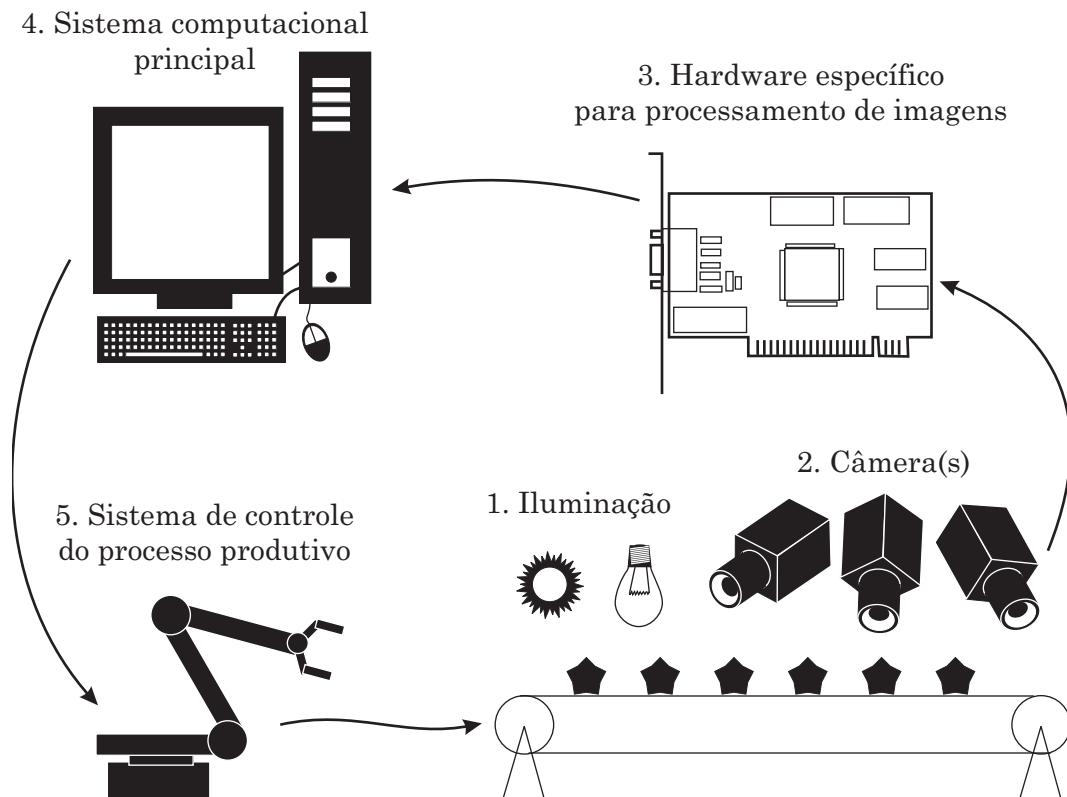

Esta seção apresenta uma visão geral da arquitetura típica de um sistema de IVA. A Fig. 2 mostra uma arquitetura típica como parte integrante de um processo produtivo industrial, composta por:

1. Sistema de iluminação contendo um ou mais emissores de luz, naturais ou artificiais;

2. Conjunto óptico-eletrônico para captura da imagem, composto por uma ou mais câmeras;

3. *Hardware* específico para processamento de imagens;

4. Sistema computacional principal;

5. Sistema de controle do processo produtivo.

### 2.4.1 Iluminação

O primeiro item da arquitetura, o sistema de iluminação, mostrado na Fig. 2 (1), tem como propósito destacar as informações de interesse no cenário ou minimizar o efeito de outras fontes de luz sobre o objeto em inspeção. Nos dois casos o foco é melhorar a qualidade da imagem capturada e, com isto, reduzir o esforço computacional necessário para extrair as características relevantes da imagem associadas com as não conformidades em relação às características esperadas para o objeto. A iluminação pode ser bastante

---

3. <http://www.st.com>

4. <http://www.trajan-software.demon.co.uk>

Figura 2: Arquitetura típica de um sistema de IVA.

simples, como a utilizada na inspeção de ferrovias (3). Neste caso a iluminação foi projetada para reduzir os efeitos da variação natural da luz nos trilhos dos trens. Para tal, foram utilizadas seis lâmpadas halógenas de 100 W com refletor tipo “spot”, sem controle de intensidade.

O sistema de iluminação também pode ser bastante complexo, como na medição de formas tridimensionais, apresentado em (13). Neste caso a iluminação é realizada através de um projetor. Durante a medição do objeto 3D, um conjunto de padrões de franjas é projetado sobre a superfície do objeto de interesse e a característica de profundidade do objeto naturalmente irá distorcer estes padrões de franjas. Neste momento, o objeto e os padrões de franjas distorcidos são capturados pela câmera sob forma de imagem digital para ser processada e gerar um modelo 3D do objeto. Outro exemplo de uso de projetores de padrões é o trabalho apresentado em (12). Este trabalho utiliza o mesmo princípio básico da triangulação entre o projetor, o objeto sob inspeção e a câmera, para determinar o formato do objeto. O diferencial deste trabalho foi o aprimoramento para aplicação em clínicas, no armazenamento digital dos modelos ortodônticos.

A iluminação também pode ser realizada utilizando *laser*. Em (9), inspeção de cones de alto-falantes, o *laser* atua com um princípio de triangulação para determinar a distância

entre o objeto e a câmera, semelhante aos sistemas que utilizam iluminação por projetores. Já em (10), inspeção de frutas em árvores, o módulo *laser* disponibiliza para a unidade de processamento as informações de distância entre o *laser* e o objeto, bem como a atenuação causada pela absorção da luz na superfície do objeto.

O último modelo que será apresentado é a iluminação multiplexada. Em (8), inspeção de PCI, são utilizadas três lâmpadas circulares com LEDs, todas com diâmetros diferentes, localizadas no topo do sistema e centralizadas com a PCI sob inspeção. Estas lâmpadas são multiplexadas no tempo, ou seja, acendem seqüencialmente, uma por vez. Logo, é necessário que a câmera capture três imagens, uma para cada lâmpada acesa, para que o processador realize a inspeção das soldas. De acordo com a quantidade de luz refletida na solda, nos três ângulos de incidência da luz, o processador será capaz de decidir se a solda está dentro dos padrões, ou não. A iluminação também pode ser multiplexada no comprimento de onda (cor da luz). Em (14) foram instalados três emissores de luz em ângulos diferentes em relação a superfície sob inspeção. Um vermelho, um verde e um azul. A luz refletida na superfície pelos três emissores é capturada por uma câmera RGB. Este tipo de câmera tem três canais de saídas independentes: um vermelho, um verde e um azul. É mostrado no trabalho (14) que, a partir da análise dessa imagem composta RGB, é possível determinar a textura da superfície sob inspeção.

## 2.4.2 Câmeras

O segundo item da arquitetura básica é o conjunto óptico-eletrônico para captura da imagem<sup>5</sup>. A função das câmeras é implementar a primeira etapa do processamento da imagem: a aquisição, conforme apresentado na seção 2.3.1. Este item da arquitetura é composto, geralmente, por uma ou mais câmeras em posições fixas, conforme apresentado na Fig. 2 (2).

Em relação ao tipo do sensor de luz utilizado na câmera, existem dois tipos básicos: CCD e CMOS. Os sensores CCD (*Charge-Coupled Devices*) são os mais utilizados em aplicações de visão computacional. A câmera CCD tem uma matriz de elementos sensíveis a luz, chamados de pixels. Logo, todos os pixels da imagem são capturados simultaneamente em valores contínuos. A digitalização de todos os pixels da imagem é realizada em uma etapa posterior. Esses sensores também têm a característica de possuir uma relação linear entre a intensidade de luz da entrada e o sinal elétrico da saída. Esta característica

5. A captura da imagem se refere ao processo de conversão da luz refletida ou emitida pelo objeto observado em um sinal elétrico. Este sinal pode ser analógico ou digital.

torna essas câmeras adequadas para aplicações de metrologia.

Já os sensores CMOS (*Complementary Metal-Oxide-Semiconductor*) convertem a imagem pixel por pixel, já no formato digital, seqüencialmente, do topo até a base da imagem. Esta característica pode ser indesejada para aplicações onde a iluminação é realizada por lâmpadas fluorescentes ou com *flash* de luz. Nestes casos a imagem pode ser adquirida com uma parte clara e outra escura. Algumas vantagens das câmeras CMOS são o baixo consumo energético, alta resolução da câmera e a alta velocidade de captura da imagem.

Quanto ao sinal de saída das câmeras, este pode ser classificado em analógico ou digital. Os padrões analógicos mais difundidos são os compostos (NTSC/PAL, EIA/CCIR), Y-C (S-Video) e RGB. Destes, os sinais NTSC e EIA são os mais comuns para a maioria das aplicações de IVA. Já os sinais Y-C e RGB fornecem imagem em qualidade superior, com as cores em canais separados. A utilização de câmeras analógicas resultam normalmente em baixa resolução da imagem, baixa taxa de aquisição (normalmente 30 quadros por segundo), sinal com mais ruídos e saída entrelaçada<sup>6</sup>. Além disto, antes de processar a imagem em computador é necessário que os sinais destas câmeras sejam digitalizados a partir de um hardware específico de aquisição de imagens.

Quanto ao formato digital, estas têm algumas vantagens sobre as analógicas. Geralmente câmeras digitais são configuráveis, podendo ser capturada a imagem com maior velocidade ou maior resolução. Além disto, há pouca perda de sinal, baixo nível de ruído e a varredura da imagem é realizada de maneira não-entrelaçada<sup>7</sup>. Os padrões mais comuns são CameraLink™ (CL), IEEE-1394 (*Firewire*), *Gigabit Ethernet* (GigE), RS-422 e RS-644. As escolhas imediatas são GigE e CL. A escolha depende da velocidade, sincronização e geografia. Somente a GigE permite longas distâncias em cabos comuns. Já a CL é mais rápida que qualquer outra interface. Além disto, somente a CL inclui facilidades para *real-time triggering*.

Quanto às cores, a câmera pode ser monocromática, colorida com um sensor ou colorida com três sensores. As câmeras monocromáticas têm um sensor único que fornece o nível de cinza. Tem a vantagem de a resolução ser 10% superior às câmeras coloridas de um sensor. Além disto, possui melhor relação sinal/ruído, melhor contraste e maior sensibilidade para baixa iluminação.

Já as câmeras coloridas de um sensor usam, geralmente, filtro de cor Bayer RGB. Esta

---

6. Um quadro é dividido em dois campos (pares e ímpares). Varre-se as linhas ímpares (1,3,5) e então as pares (2,4,6). Estes campos são então integrados para produzir um quadro completo

7. *Progressive Scan* - Técnica que “varre” a tela inteira em uma única passada, transmitindo todas as linhas da imagem a cada atualização

tecnologia é de baixo custo e se integra facilmente aos sistemas de IVA. Porém a resolução é inferior às câmeras coloridas de três sensores. Esta última tecnologia, com três sensores, utiliza um prisma para dividir a luz branca em três componentes. Como vantagem, estes sensores tem melhor resolução de cor. Por outro lado, esta tecnologia é mais cara e possui sensibilidade mais baixa.

Por fim, existem as câmeras inteligentes (*SmartCams*). Estas câmeras integram o *hardware* e o *software* dentro da própria câmera. Fazem parte da arquitetura destas câmeras, além do sensor, um processador, *frame grabber*, interface serial, ethernet ou USB, entrada para *triggers* de alta velocidade, E/S para CLPs, memória RAM e cartões de memória SD.

#### 2.4.3 *Hardware* específico para processamento de imagem

O terceiro item da arquitetura, mostrado na Fig. 2 (3), é o *hardware* específico para executar parte do processamento da imagem. De fato, este item é normalmente utilizado para implementar o pré-processamento da imagem, conforme apresentado na seção 2.3.1. Porém, sobretudo nos casos que necessitam desempenho superior, este *hardware* específico também é utilizado para implementar as três etapas do processamento de nível intermediário: segmentação, representação e descrição da imagem, conforme apresentado na seção 2.3.2

Nos sistemas de IVA, a implementação de todas as etapas do processamento da imagem exclusivamente em *software*, geralmente, não é suficiente para atingir os requisitos de desempenho para a aplicação. Visando solucionar este gargalo, cada vez mais está sendo implementada parte do algoritmo de processamento da imagem em *hardware*. A seguir serão vistas algumas características da implementação em ASIC, DSP e FPGA. A escolha da tecnologia a ser utilizada deverá ter base no tamanho do chip, potência dissipada, custo e desempenho. Além disto, é importante observar a flexibilidade do uso, ambiente de programação e pacotes de *softwares* disponíveis. Estas últimas características são de grande relevância para os desenvolvedores do sistema de IVA.

##### ASIC

A primeira tecnologia para realizar o processamento da imagem em *hardware* é construir um circuito integrado (CI) exclusivo para a aplicação de IVA utilizando um ASIC (*Application Specific Integrated Circuit* - Circuito integrado para aplicação específica).

Atualmente a forma mais eficiente de desenvolver um ASIC é a utilização de núcleos IP<sup>8</sup> (*Intellectual Property* — Propriedade Intelectual) disponíveis no mercado. O tempo de desenvolvimento é reduzido por que as células adquiridas prontas já foram testadas em diferentes tecnologias de fabricação. De maneira simplificada, o design de um ASIC consiste na montagem de blocos IP, inserindo alguma lógica entre estes blocos para realizar a interface. A principal desvantagem do ASIC é que o circuito geralmente tem sua utilização limitada em uma aplicação específica.

Para reduzir a inflexibilidade, alguma programabilidade pode ser incorporada no ASIC. Uma opção é utilizar núcleos IP de processadores. Algumas empresas, como a ARM e a Synopsys, disponibilizam núcleos DSP RISC, já projetados para aplicações embarcadas. Um produto interessante oferecido pela Synopsys é o núcleo ARC<sup>9</sup>. Este é um processador de 32 bits, muito pequeno (em área ocupada) e de alta velocidade (com *clock* acima de 100 MHz). Além disto, a Synopsys disponibiliza uma ferramenta que permite a configuração do processador ARC de acordo com os requisitos da aplicação. Por exemplo, dependendo da aplicação, a ferramenta pode configurar o processador com maior *cache* de instruções e disponibilizar mais memória RAM ou registradores para uso geral. O código VHDL é então gerado e poderá ser sintetizado.

Outra forma de reduzir a inflexibilidade do ASIC é implementar em um único chip diversos algoritmos de processamento de imagens comuns para um domínio de aplicações. Por exemplo, um CI pode ser desenvolvido para realizar a transformada rápida de Fourier (*Fast Fourier Transformer - FFT*), detecção de bordas, transformada de Hough, entre outros. Com isto, o ASIC poderá ser reutilizado; para tal sendo necessário apenas modificar alguns sinais de entrada, parâmetros informados pelo sistema computacional principal ao chip.

## DSP

Uma alternativa de menor custo é utilizar um DSP ao invés de confeccionar um ASIC. O uso de placas com DSP tem sido extensivamente utilizado em aplicações de visão industrial com requisitos de tempo real. Uma família de placas com DSP muito popular é a “Connected Media Processor”, da NXP Semiconductors<sup>10</sup> (antiga Philips Semiconductors). Estas placas tem interface PCI e usa processadores da série TriMedia, que tem tecnologia VLIW (*Very Long Instruction Word*) voltada para aplicações multimídia, com

8. No design de semicondutores, *IP Core*, ou núcleo IP, é um bloco reutilizável de lógica, células ou layout de chip. Um núcleo IP pode ser desenvolvido e licenciado para terceiros.

9. <http://www.synopsys.com/IP/ConfigurableCores/ARCProcessors/Pages/default.aspx>

10. <http://www.nxp.com>

arquitetura Harvard e que permite processar eficientemente fluxos de dados de vídeo e de áudio. O *clock* para este processador pode ser superior à 500 MHz.

## FPGA

FPGAs são competitivos em relação aos ASICs em termo de capacidade e desempenho. Uma vantagem do FPGA é permitir, rapidamente, testar o sistema em condições reais. Outra vantagem é que, quando comparado ao ASIC, o FPGA é eletricamente reprogramável. Ou seja, o FPGA pode ser reusado no caso de modificações nos requisitos do sistema ou simplesmente quando ocorrer algum erro no processo de design do FPGA. Adicionalmente, é possível inserir um núcleo IP no FPGA assim como realizado no ASIC (por exemplo, um ARM ou um PowerPC com memória RAM e periféricos).

A Acromag<sup>11</sup>, por exemplo, desenvolve uma ampla linha de placas de processamento de imagens para uso industrial baseado em FPGA, tanto Xilinx®, quanto Altera®. A Acromag também disponibiliza para *download* diversos códigos com algoritmos para processamento de imagem. Outro exemplo é a placa utilizada neste trabalho de mestrado, a “Altera Digital Camera Development Platform”, da Terasic<sup>12</sup>. Esta é uma placa desenvolvida para fins educacionais que utiliza um FPGA Cyclone II, da Altera. Além do FPGA, a placa disponibiliza uma câmera digital de 5 Mpixels, um display LCD de 4,3”, interface USB, SD Card, memória RAM, entre outros periféricos.

### 2.4.4 Sistema computacional principal

O sistema computacional principal tem como função implementar, sobretudo, as etapas de processamento de alto nível: reconhecimento e interpretação da imagem, conforme apresentado na seção 2.3.3.

O sistema computacional principal, mostrado na Fig. 2 (4), geralmente contém um processador de uso geral, por exemplo um Pentium®, da Intel®, ou um Athlon®, da AMD®, que está instalado em um PC. Na realidade, desde o lançamento das instruções MMX com a tecnologia SIMD no Pentium, em 1997, processadores de uso geral estão executando mais etapas do processamento da imagem. De fato, em alguns casos, principalmente aqueles que não necessitam de processamento em tempo real, o processamento da imagem é totalmente realizado por um processador de uso geral. Por exemplo, na inspeção de garrafas (4), de frutas em árvores (10) e de soldas em PCI (8).

---

11. <http://www.acromag.com/>

12. <http://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=53&No=296>

A principal vantagem do processador de uso geral é o ambiente de programação, que permite que o programa seja desenvolvido sem nenhum conhecimento prévio da arquitetura do computador. Por outro lado, o processador de uso geral consome mais energia que as placas específicas para processamento da imagem e, geralmente, são proibitivos para as aplicações embarcadas.

#### 2.4.5 Sistema de controle, sensores e atuadores do processo produtivo

O último item da arquitetura básica da IVA é mostrado na Fig. 2 (5). Este sistema é composto por um controlador industrial, geralmente um CLP (Controlador Lógico Programável), sensores e atuadores. Este conjunto de elementos tem a função básica de identificar o posicionamento do objeto antes da inspeção e atuar mecanicamente no objeto visando mudar a sua posição ou forma após a inspeção.

Segundo a Associação Brasileira de Normas Técnicas (ABNT), um CLP é um equipamento eletrônico digital com *hardware* e *software* compatíveis com aplicações industriais. Adicionalmente, é um dispositivo com funcionalidades semelhante as de um microcontrolador, com seus periféricos, porém adaptado para ambientes industriais.

Os elementos sensores são dispositivos que recebem um sinal, seja óptico, sonoro, térmico ou proveniente de qualquer outra forma de energia, convertem para um sinal elétrico e condicionam este sinal para uso pelo CLP ou pelo sistema computacional principal do sistema de IVA. Os principais sensores utilizados em IVA são destinados a detectar a presença do objeto para iniciar a inspeção e, geralmente, estes sensores têm natureza capacitiva, indutiva ou óptica.

Por fim, os elementos atuadores completam a IVA permitindo mudanças na posição ou forma do objeto durante ou após a inspeção. Os atuadores mais comuns em IVA são os de cilindro pneumático, cilindro hidráulico e motores. Ainda são exemplos de atuadores: garras, pulverizadores de tinta e eletroímãs.

### 2.5 Exemplos de IVA dimensional

O primeiro trabalho a ser apresentado visa melhoramentos em uma aplicação popular e muito demandada: a inspeção e classificação de soldas em placas de circuito impressa (PCI). Um sistema típico para esta aplicação consiste em um sistema de iluminação apro-

priado e uma câmera no topo do sistema de inspeção (8). O processamento da imagem da PCI consiste em duas etapas principais. Na primeira, um pré-processamento é realizado para remover os ruídos da imagem e tornar a identificação das soldas mais fácil. Então, na segunda etapa, as soldas são classificadas de acordo com o tipo de defeito. A classificação normalmente é realizada a partir da quantidade de solda presente na placa. Quatro classes foram definidas: (I) solda na quantidade normal, nominada como boa, (II) excesso de solda, (III) solda insuficiente e (IV) sem solda. Resultados de simulação nos modelos geométricos das soldas têm mostrado que a classificação eficiente pode ser atingida somente após uma seleção de características ótimas, isto para que as classes não se sobreponham (24). Pesquisas tem mostrado que técnicas baseadas no histograma (25) tem desempenho melhor que técnicas baseadas na extração de características baseada na imagem em duas e três dimensões. Muitas inspeções de PCI utilizam redes neurais no projeto dos classificadores.

Uma técnica para o problema de cortar partes com formas irregulares (inclusive formas côncavas) em folhas bidimensionais (papel, couro, tecido, etc.) é visto em (26). Um sistema de visão de máquina é utilizado para adquirir as imagens das partes irregulares que serão reproduzidas industrialmente em maior escala posteriormente. Após a captura da imagem, é realizada a detecção e poligonarização das bordas. Ou seja, a visão de máquina converte um pedaço de folha cortado irregularmente em um polígono no computador. A partir desta etapa, um algoritmo genético é usado para gerar diversas combinações de posicionamento das peças irregulares dentro da folha inteira, visando minimizar as perdas de material no processo de corte destes pedaços irregulares. Esta técnica é particularmente útil para as indústrias de couro e vestuário, onde cortes irregulares são normalmente utilizados para a confecção do produto final.

Um sistema de IVA para localização de frutas esféricas em árvores, sob condições naturais, é apresentado em (10). O sistema utiliza um *laser* que fornece informações de distância entre o *laser* e o objeto sob inspeção, e de atenuação da luz, que expressa a quantidade de luz absorvida pela superfície do objeto. A partir destas informações, um algoritmo é utilizado para identificar formas esféricas e suas posições na árvore. Resultados experimentais mostram que aproximadamente 85% das frutas visíveis e 55% das parcialmente visíveis foram corretamente detectadas. A tecnologia foi embarcada no sistema robótico “AGRIBOT” visando a coleta automática de frutas.

Uma atividade muito comum em IVA é detectar linhas e círculos em imagens. A técnica apresentada em (27) se concentra na detecção de bordas e identificação de par-

tes circulares, inclusive círculos irregulares. Para tal, uma transformada de Hough em dois estágios é utilizada. Outro exemplo de detecção de formas primárias pode ser visto em (28). Neste artigo são detectadas as elipses da imagem, inclusive para aplicação de reconhecimento facial. Para tal, assim como em (27), é necessário utilizar um algoritmo de detecção de bordas associado a uma transformada de Hough.

Um exemplo de IVA dimensional em tempo real pode ser visto em (18). Nesta aplicação são comparados produtos impressos em alta resolução, com alto grau de similaridade, onde a identificação de diferenças mínimas é bastante difícil para humanos, principalmente quando este deve ser realizado em tempo real. Um algoritmo original, baseado em operações morfológicas, facilita a detecção de imperfeições em uma resolução capaz de identificar irregularidades do tamanho de um pixel. O sistema pode ser aplicado para a inspeção de cédulas, cheques e outros documentos bancários, considerando os requisitos para validação das impressões produzidas.

O último trabalho que será apresentado como exemplo de IVA dimensional nesta seção é a inspeção de rosas de parafusos (29). Neste trabalho é verificado se a rosca atende aos padrões do fabricante. Um algoritmo para detecção de bordas, baseado em interpolação linear para obter uma resolução sub-pixel, é aplicado para detectar as bordas na região de interesse. Em seguida, é verificado se a borda está inteiramente compreendida dentro da faixa de tolerância, definida pelo fabricante. O sistema foi testado em linha de produção e obteve desempenho melhor que outros métodos competitivos, inclusive a medição manual.

## 2.6 Análise do capítulo

Várias indústrias estão envolvidas no desenvolvimento de sistemas de visão para automatizar a inspeção das características geométricas de objetos. Isto se dá por que existe uma ampla gama de aplicações para a IVA dimensional e, para cada domínio de aplicações, existem diferentes requisitos provenientes das características ambientais desiguais entre aplicações e das diversas formas de respostas esperadas do sistema de IVA. Logo, não existem sistemas de visão industrial capazes de abranger todas as tarefas, em todos os campos de aplicação.

De um modo geral, é necessário que os sistemas de IVA identifiquem que informações são importantes nas imagens, extraí-las e utilizá-las para classificar os objetos. Vários trabalhos analisados utilizaram estas informações para classificar o objeto sob inspeção entre “bom” e “ruim”, com a confiabilidade (taxa de acerto) adequada para a aplicação.

É de responsabilidade do sistema computacional manter o sistema confiável, porém, o sistema de iluminação e de aquisição da imagem influencia significativamente o uso de recursos computacionais necessários para manter a confiabilidade.

O sistema de IVA também deve ser robusto e uma das principais dificuldades para obtenção desta característica é a composição do plano de fundo por outros objetos com diversas formas, texturas e iluminação. A segmentação pode ser uma das atividades mais complexas do processamento da imagem e, se utilizado um algoritmo inadequado, quase sempre resulta em um comprometimento completo do sistema de IVA.

Por fim, um sistema de visão industrial deve ser rápido e compacto. Desta forma, existe uma demanda crescente por sistemas de IVA embarcados com *hardware* específico para processamento de imagens.

### 3 *Trabalhos relacionados*